7.8.3-4一般时序电路的VHDL描述

7.8.3习题7-41电路设计

7.8.4串行输入信号中1的个数奇偶判决电路设计

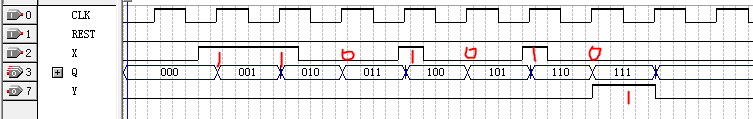

7.8.5课堂进行1101010序列检测电路设计

--********************************************

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

--*********************************************

ENTITY xulie11101010 is --记得填入实体名,也是本文件名

PORT(CLK,X,REST :in std_logic; --输入输出引脚说明

--:in std_logic_vector( downto 0);

Y:OUT std_logic;

Q:OUT std_logic_vector( 2 downto 0));

END xulie11101010 ; --记得填入实体名,也是本文件名

--*********************************************

ARCHITECTURE abc OF xulie11101010 IS

TYPE STATE IS (S0,S1,S2,S3,S4,S5,S6,S7) ; --记得填入实体名,也是本文件名

--signal :std_logic_vector( downto 0);

signal ST :STATE;

BEGIN

PROCESS(CLK,X,REST)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF REST='1' THEN ST<=S0;

ELSE

CASE ST IS

WHEN S0 => IF X='1' THEN ST <= S1;Q<="001";Y<='0';

ELSE ST<=S0;Q<="000";Y<='0';

END IF;

WHEN S1 => IF X='1' THEN ST <= S2;Q<="010";Y<='0';

ELSE ST<=S0;Q<="000";Y<='0';

END IF;

WHEN S2 => IF X='0' THEN ST <= S3;Q<="011";Y<='0';

ELSE ST<=S2;Q<="010";Y<='0';

END IF;

WHEN S3 => IF X='1' THEN ST <= S4;Q<="100";Y<='0';

ELSE ST<=S0;Q<="000";Y<='0';

END IF;

WHEN S4 => IF X='0' THEN ST <= S5;Q<="101";Y<='0';

ELSE ST<=S2;Q<="010";Y<='0';

END IF;

WHEN S5 => IF X='1' THEN ST <= S6;Q<="110";Y<='0';

ELSE ST<=S0;Q<="000";Y<='0';

END IF;

WHEN S6 => IF X='0' THEN ST <= S7;Q<="111";Y<='1';

ELSE ST<=S2;Q<="010";Y<='0';

END IF;

WHEN S7 => IF X='1' THEN ST <= S1;Q<="001";Y<='0';

ELSE ST<=S0;Q<="000";Y<='0';

END IF;

WHEN OTHERS => NULL;

END CASE;

END IF;

END IF;

END PROCESS;

end abc;

7.8.6习题7-45电路设计

7.8.7习题7-11电路用状态机设计

7.8.8习题8-15电路设计