3.10 Demand Segment with Paging Management

1. Idea

Each program has a segment table, with one descriptor per segment. The segment table is itself a segment and is paged. A segment descriptor contains an indication of whether the segment is in main memory or not. If any part of the segment is in memory, the segment is considered to be in memory, and its page table will be in memory.

Each segment is an ordinary virtual address space and is paged in the same way as the nonsegmented paged memory described earlier in earlier chapters.

2. Address structure

An address consists of two parts: the segment number and the address within the segment (offset). The offset is further divided into a page number and a page offset.

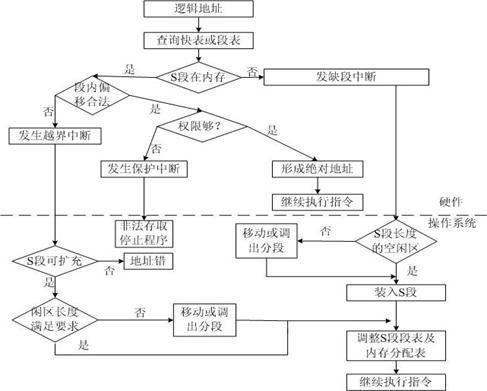

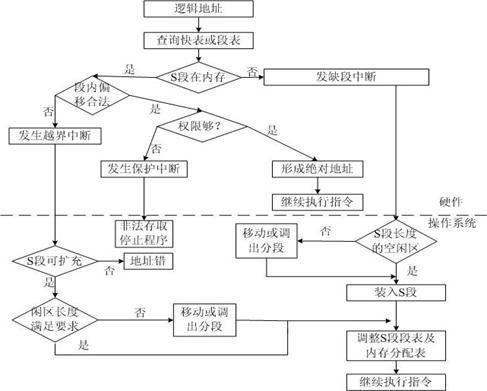

3.The address relocation

When a memory reference occurs, the following algorithm is carried out.

1. The segment number used to find segment descriptor.

2. Check is made to see if the segment’s page table is in memory.

1. If not, segment fault occurs.

2. If there is a protection violation, a fault (trap) occurs.

3. Page table entry for the requested virtual page examined.

1. If the page itself is not in memory, a page fault is triggered.

2. If it is in memory, the main memory address of the start of the page is extracted from the page table entry

4. The offset is added to the page origin to give the main memory address where the word is located.

The read or store finally takes place.

1.In the segmentation with paging method, we need to visit the main memory three times for getting the data or the instructions. The first time is for the ( ) from the memory, the second time is for the ( ), the third time is for the( ).

Solution: the page table start address block number instructions or data

2.In the segmentation with paging method, each program has a ( ) table and a ( ) table.

Solution: segment page

The Burroughs Corporation B5000 computer was one of the first to implement segmentation, and "perhaps the first commercial computer to provide virtual memory"[4]based on segmentation. The later B6500 computer also implemented segmentation; a version of its architecture is still in use today on the Unisys ClearPath Libra servers.

The GE-645 computer, a modification of the GE-635 with segmentation and paging support added, was designed in 1964 to support Multics.

The Intel iAPX 432,[5] begun in 1975, attempted to implement a true segmented architecture with memory protection on a microprocessor.

Prime, Stratus, Apollo, IBM System/38, and IBM AS/400 computers use memory segmentation.

The memory segmentation used by early x86 processors, beginning with the Intel 8086, does not provide any protection. Any program running on these processors can access any segment with no restrictions. A segment is only identified by its starting location; there is no length checking.

Segmentation in the Intel 80286 and later provides protection: with the introduction of the 80286, Intel retroactively named the sole operating mode of the previous x86 CPU models "real mode" and introduced a new "protected mode" with protection features. For backward compatibility, all x86 CPUs start in "real mode" with no memory protection, fixed 64 KiB segments, and only 20-bit (1024 KiB) addressing. An 80286 or later processor must be switched into another mode by software in order to use its full address space and advanced MMU features.

In the x86 implementation of segmentation the segment table, rather than pointing to a page table for the segment, contains the segment address in linear memory. This address is then mapped to a physical address using a separate page table. Unlike other paged implementations of segmentation this prevents segments from dynamically growing in size.

The x86-64 architecture does not use segmentation in long mode (64-bit mode). Four of the segment registers: CS, SS, DS, and ES are forced to 0, and the limit to 264. The segment registers FS and GS can still have a nonzero base address. This allows operating systems to use these segments for special purposes.