二 常用组合逻辑电路

一、加法器与比较器

1.加法器

1)加法器的概念

加法器是计算机实现加、减、乘、除等算术运算的基本单元。当参与运算的两个二进制数相加时,如果仅考虑两个1位二进制数相加,不考虑低位进位数时,称这种加法运算电路为半加器;如果在考虑两个1位二进制数相加时,还考虑来自低位进位数相加的运算电路为全加器;如果进行多位二进制数相加时,则需将多个全加器级联组成多位加法器,实现多位加法运算的电路,称为加法器。

2)全加器的逻辑功能

(1)串行进位加法器。

低位全加器进位输出端CO依次和相邻高位进位输入端CI相连,显然,高位必须等到低位运算完成才能进行运算,运算速度较慢。

(2)并行进位(超前进位)加法器。

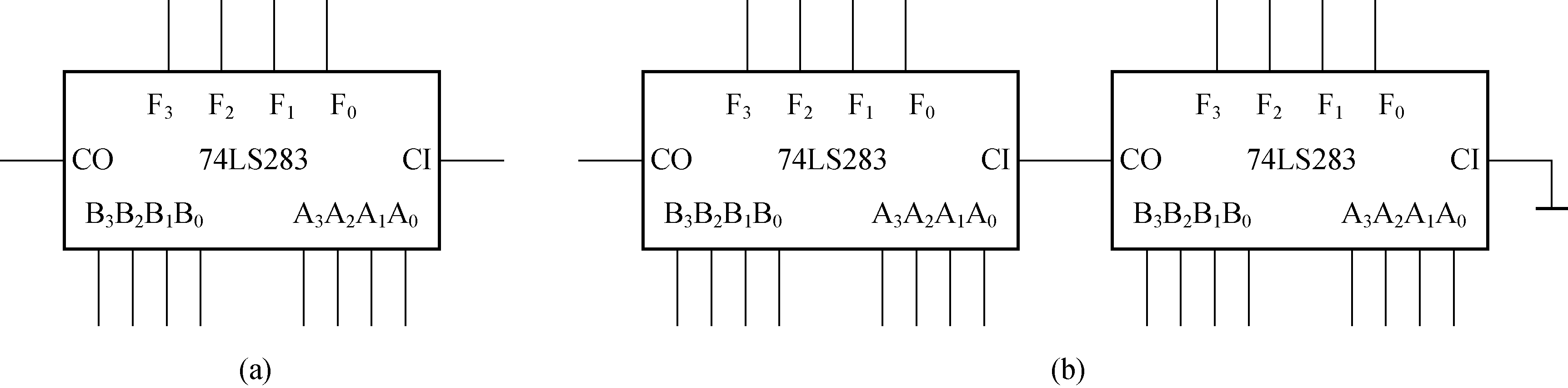

图10-8 74LS283四位超前进位加法器

2.数值比较器

1)基本原理

用来比较两个n位二进制数大小或是否相等的逻辑电路,称为数值比较器。两个 n位二进制数比较时,应从高位到低位逐位进行比较,高位数相等时,才能进行低位数的比较。当比较到某一位数值不等时,其结果就是两个n位二进制数的比较结果。

2)典型芯片

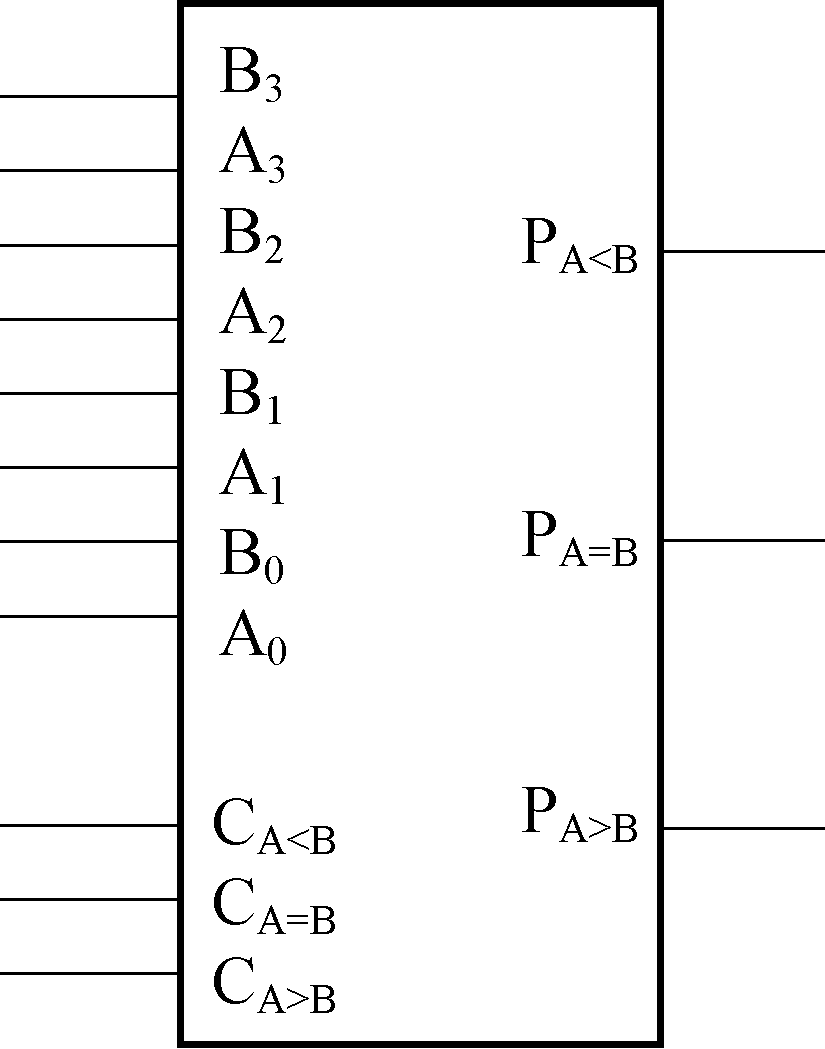

74LS85芯片的引线图如图10-9所示。

图10-9 74LS85引线图

3)比较器的级联

四位比较器可直接用来比较两个四位或小于四位的二进制整数的大小。当两个待比较的数的位数超过四位时,往往要将多个比较器级联使用。

二、编码器

1.二进制编码器

这种编码器有一个特点:任何时刻只允许输入一个有效信号,不允许同时出现两个或两个以上的有效信号,因而其输入是一组有约束(互相排斥)的变量。

2.二-十进制(BCD)编码器

在数字电子系统中,所处理的数据都是二进制的,而在实际生活中常用十进制数,将十进制数0~9转换成一组二进制代码的逻辑电路称为二十进制编码器。它的输入是代表 0~9这10个数字的状态信号,有效信号为1(即某信号为1时,则表示要对它进行编码),输出是相应的BCD码,因此也称10线4线编码器。它和二进制编码器特点一样,任何时刻只允许输入一个有效信号。

3.优先编码器

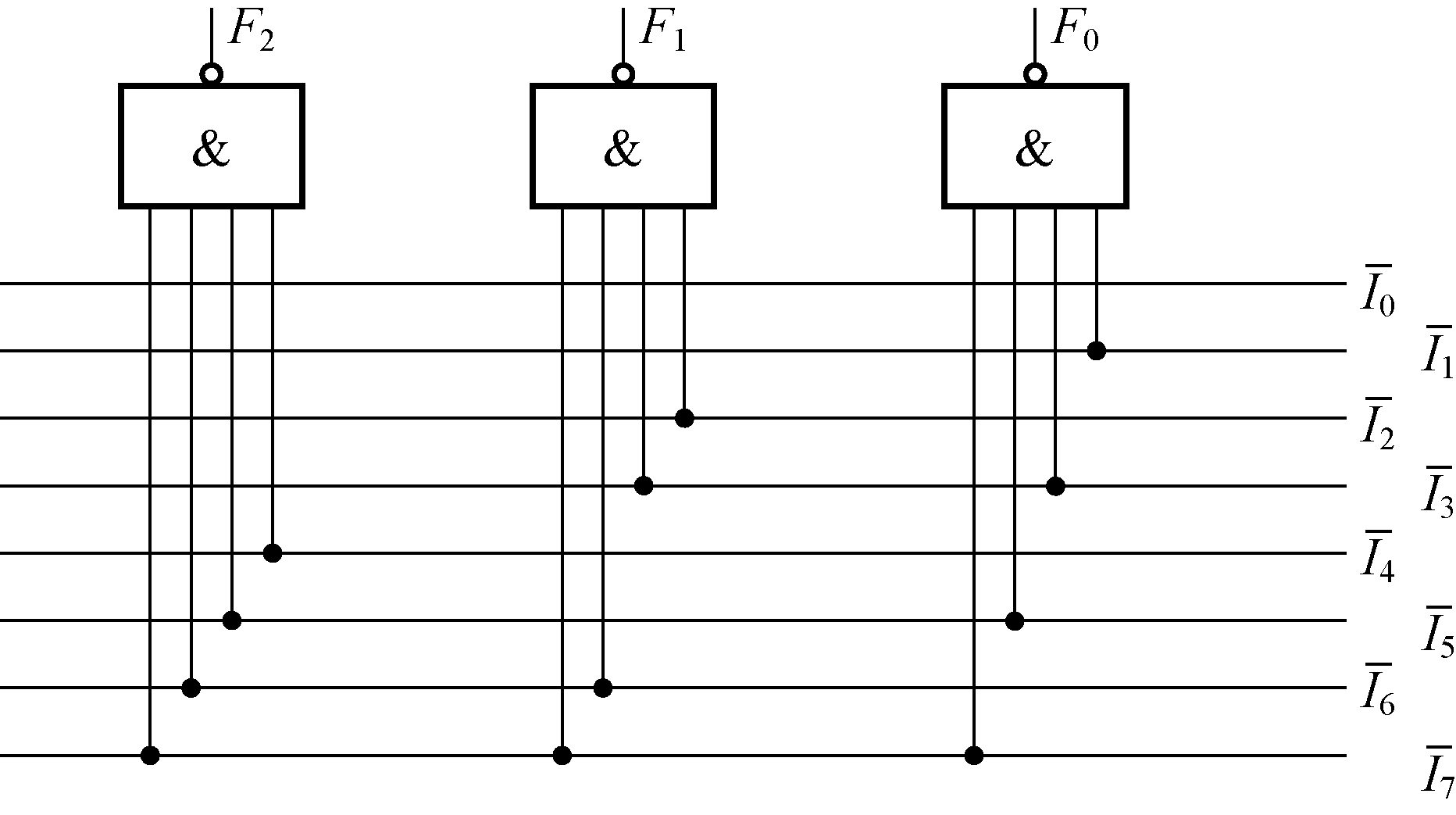

在同一时间内,当有多个输入信号请求编码时,只对优先级别高的信号进行编码而不会对级别低的信号编码的逻辑电路,称为优先编码器。常用的集成优先编码器有74LS148(8线-3线)和74LS147(10线-4线)两种。

图10-13 8线-3线优先编码器74LS148功能简图

三、译码器

1.译码器的概念

译码与编码是相反的过程,是将二进制代码表示的特定含义翻译出来的过程。能实现译码功能的组合逻辑电路称为译码器。

1)二进制译码器

二进制译码器是将输入的二进制代码的各种状态按特定含义翻译成对应输出信号的电路,也称为变量译码器。若输入端有n位,代码组合就有2n个,可译出2n个输出信号。

2)二-十进制译码器

二-十进制译码器是完成同一数据的不同代码之间的相互交换的电路,所以也称为码制变换译码器。

3)显示译码器

显示译码器用于将字符信息的代码翻译成相应的字符信息,并显示的组合电路,它由译码器和驱动电路组成。其输入一般是BCD码,输出为七段码a~g,用于驱动显示器。数字显示器种类很多,按发光材料不同可分为荧光显示器、半导体发光二极管显示器(LED)和液晶显示器(LCD)等;按显示方式不同可分为字表重叠式、分段式和点阵式等。

2.集成二进制译码器的功能介绍及应用

1)74LS138的功能介绍

2)74LS138的应用

(1)实现存储系统的地址译码。

(2)实现逻辑函数。

(3)带使能端的译码器可用作数据分配器或脉冲分配器

3.显示译码器

1)字符显示器

分段式显示是将字符由分布在同一平面上的若干段发光笔画组成。电子计算器、数字万用表等显示器都是显示分段式数字,而LED数码显示器是最常见的,通常有红、绿、黄等颜色。LED的死区电压较高,工作电压大约为1.5~3 V,驱动电流为几十毫安。

2)中规模集成BCD七段显示译码驱动器

四、数据选择器

1.数据选择器的概念

数据选择器又称多路选择器或多路开关,它是根据地址码的要求,从多路输入(数据)中选择其中一路输出的逻辑电路。按照输入端数据的不同有四选一、八选一、十六选一等形式。

2.数据选择器的原理