一、实验目的

1、掌握半导体静态随机存储器RAM的特性和使用方法。

2、掌握地址和数据在计算机总线的传送关系。

3、了解运算器和存储器如何协同工作。

二、实验设备

计算机组成原理实验系统一套,PC机一台。

三、预习要求

预习半导体静态随机存储器6116的功能。

四、实验原理

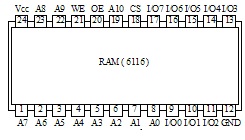

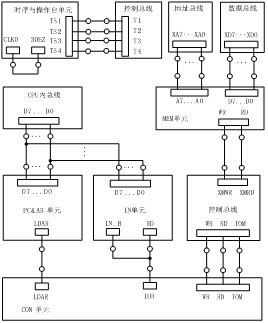

实验所用的静态存储器由一片6116(2K×8bit)构成(位于MEM单元),如图2-1所示。6116有三个控制线:CS(片选线)、OE(读线)、WE(写线),其功能如表2-1所示,当片选有效(CS=0)时,OE=0时进行读操作,WE=0时进行写操作,本实验将CS常接地。

图2-1 SRAM 6116引脚图

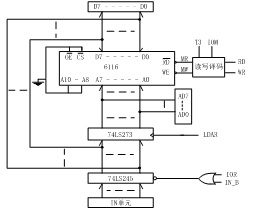

由于存储器(MEM)最终是要挂接到CPU上,所以其还需要一个读写控制逻辑,使得CPU能控制MEM的读写,实验中的读写控制逻辑如图2-2所示,由于T3的参与,可以保证MEM的写脉宽与T3一致,T3由时序单元的TS3给出(时序单元的介绍见附录2)。IOM用来选择是对I/O还是对MEM进行读写操作,RD=1时为读,WR=1时为写。

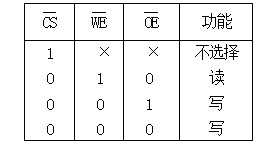

表2-1 SRAM 6116功能表

图2-2 读写控制逻辑

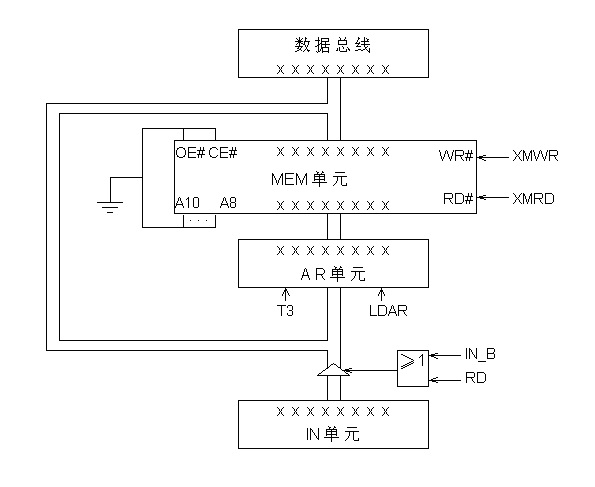

实验原理图及数据通路图如图2-3、2-4所示,存储器数据线接至数据总线,数据总线上接有8个LED灯显示D7…D0的内容。地址线接至地址总线,地址总线上接有8个LED灯显示A7…A0的内容,地址由地址锁存器(74LS273,位于PC&AR单元)给出。数据开关(位于IN单元)经一个三态门(74LS245)连至数据总线,分时给出地址和数据。地址寄存器为8位,接入6116的地址A7…A0,6116的高三位地址A10…A8接地,所以其实际容量为256字节。

图2-3 存储器实验原理图

图2-4 数据通路图

实验箱中所有单元的时序都连接至时序与操作台单元,CLR都连接至CON单元的CLR按钮。实验时T3由时序单元给出,其余信号由CON单元的二进制开关模拟给出,其中IOM应为低(即MEM操作),RD、WR高有效,MR和MW低有效,LDAR高有效。

五、实验内容

掌握静态RAM的的读写方式,往RAM的任意地址里存放数据,然后读出并检查结果是否正确。

图2-5 实验接线图

六、实验步骤

(1)关闭实验系统电源,按图2-5连接实验电路,并检查无误,图中将用户需要连接的信号用圆圈标明。

(2)将时序与操作台单元的开关KK1、KK3置为运行档、开关KK2置为‘单步’档。

(3)将CON单元的IOR开关置为1(使IN单元无输出),打开电源开关,如果听到有‘嘀’报警声,说明有总线竞争现象,应立即关闭电源,重新检查接线,直到错误排除。

(4)往存储器写数据:

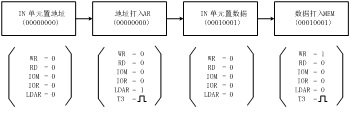

由前面的存储器实验原理图(图2-3)可以看出,由于数据和地址由同一个数据开关给出,因此数据和地址要分时写入,先写地址,具体操作步骤为:先关掉存储器的读写(WR=0,RD=0),数据开关输出地址(IOR=0),然后打开地址寄存器门控信号(LDAR=1),按动ST产生T3脉冲,即将地址打入到AR中。再写数据,具体操作步骤为:先关掉存储器的读写(WR=0,RD=0)和地址寄存器门控信号(LDAR=0),数据开关输出要写入的数据,打开输入三态门(IOR=0),然后使存储器处于写状态(WR=1,RD=0,IOM=0),按动ST产生T3脉冲,即将数据打入到存储器中。写存储器的流程如图2-6所示(以向00地址单元写入11H为例):

图2-6 写存储器流程图

(5)依据上述流程,给存储器的00H、01H、02H、03H、04H地址单元中分别写入数据11H、12H、13H、14H、15H。

(6)读出存储器数据:

同写操作类似,也要先给出地址,然后进行读,地址的给出和前面一样,而在进行读操作时,应先关闭IN单元的输出,然后使存储器处于读状态,此时数据总线上的数即为从存储器当前地址中读出的数据内容。

(7)请参照图2-6写存储器的流程图自行写出读存储器的流程,并读出已写入的数据,验证其正确性。