1.2 MCS-51单片机的结构

MCS-51单片机的典型芯片是8030、8051、8751。8051内部有4KB ROM,8751内有4KB EPROM,8031片内务ROM;除此之外,三者的内部结构相同。因此以8051为例,说明本系列单片机的内部组成及信号引脚。

1.2.1 8051单片机的基本组成

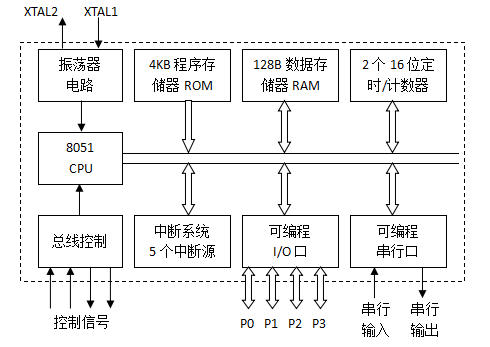

8051单片机的基本组成如图1-1所示。

图1-1 8051单片机的结构框图

由图1-1可见,8051单片机主要由以下几个部分组成:

(1)CPU

8位的微处理器,包括运算器、控制器和部分寄存器,其功能是负责执行算术和逻辑运算。

(2)存储器

● 程序存储器ROM:大小为4KB,用于存放程序,可外扩至64KB;

● 数据存储器RAM:大小为128B,用于存放数据,可外扩至64KB;

● 特殊功能寄存器SFR:51单片机共有21个特殊功能寄存器,详情见1.3.3节。

(3)4个并行I/O口

分别记为P0、P1、P2、P3,每个端口均为8位。

(4)2个16位的定时/计数器

分别记为T/C0和T/C1,既可以工作在定时状态,也可以工作在计数状态。在实际中,根据具体情况进行设置。

(5)一个全双工异步串行口

(6)中断系统

51单片机共有5个中断源入口,其中2个为外中断,3个为内中断。

(7)总线控制

如复位信号RST、地址锁存信号ALE等。按照单片机中总线的功能不同,其总线可分为数据总线、地址总线和控制总线。

(8)振荡器电路

CPU所处理的信号为数字信号,根据数字电子技术中所学知识,可知数字信号的处理是在时钟脉冲信号的作用下实现的。这里的振荡器电路就是为了产生时钟信号而设置的。

1.2.2单片机的CPU

MCS-51的CPU包括两部分:运算部件和控制器。

(1)运算部件

运算部件组成:包括算术逻辑部件ALU、布尔处理器、累加器A、寄存器B、暂

存器以及程序状态字寄存器PSW等。

运算部件功能:是实现数据的算术逻辑运算、位变量处理和数据的传送操作。

ALU的功能:可以对8位变量进行逻辑“与”、“或”、“异或”、循环、求补和清零

等基本操作,还可以进行加、减、乘、除等基本运算。还可对位(BIT)变量进行布尔处理,如置位、清零以及逻辑“与”、“或” 等操作。

累加器A: 是一个8位的累加器(也可以写为ACC),绝大部分运算和操作都同A有关。

寄存器B: 是专为执行乘法和除法操作而设置的,一般情况下也可以作为暂存

器使用。

(2)控制器(Controler)

控制器是单片机的神经中枢,以振荡器的频率位基准,产生CPU时序,对指令(Command)进行译码,然后发出各种控制信号,实现各种操作。

1.2.3 MCS-51单片机的引脚及其功能

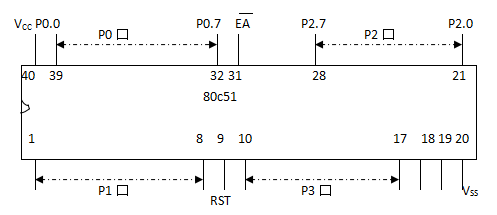

MCS-51是标准的40引脚双列直插式集成电路芯片,引脚排列参见图1-2。

图 1-2 MCS-51单片机的引脚

(1)电源

1)VCC (40)——芯片电源,接+5V;(4.5~5.5)

2)VSS (20)——电源地。

(2)时钟引脚

XTAL1(18)、XTAL2(19)——外接晶体振荡或外接脉冲。(P42)

(3)控制线

RST(9)——复位引脚。(Reset),高电平有效。

![]() EA——片内外ROM选择

EA——片内外ROM选择

![]() EA=1,选择片内ROM;

EA=1,选择片内ROM;

![]() EA=0,选择片外ROM。

EA=0,选择片外ROM。

★注意★:控制信号线写法上的差别。有“非”表示低电平起作用,反之是高电平起作用。

(4)I/O口线

P0口:8位双向I/O口。在访问外部存储器时,P0口可用于分时传送低8位地址

总线和8位数据总线。能驱动8个LSTTL门。

P1口:8位准双向I/O口(“准双向”是指该口内部有固定的上拉电阻)。能驱动

4个LSTTL门。

P2口:8位准双向I/O口。在访问外部存储器时,P2口可用于高8位地址总线。能驱动4个LSTTL门。

P3口:8位准双向I/O口。能驱动4个LSTTL门。P3口还有第二功能。

1.2.4 MCS-51单片机的存储器结构

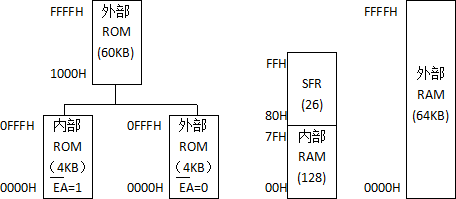

MCS-51单片机的组织结构可以分为三个不同的存储空间,分别是:

64KB的程序存储器(ROM),包括片内和片外;

64KB的外部数据存储器(外RAM);

内部数据存储器(内RAM)。

这三种不同的存储器在物理结构上是相互独立的,它们有各自的寻址系统、控制信号,CPU是通过不同的指令来访问或操作这些存储器。其结构如图1-3所示。

图 1-3 单片机的存储器结构