这是一个重要的实验,第一个实验内容对应智能小车车轮电机的PWM调制设计,第二个实验内容对应智能小车的控制系统设计。

实验项目 | 用PLD设计时序逻辑电路(一) |

实验目的 | 1.熟悉用PLD设计时序逻辑电路的方法。 2.掌握用PLD实现方波输出分频器的方法。 |

实验要求 | 掌握PLD设计时序逻辑电路的方法 |

实验内容 | 1.用VHDL语言和PLD设计一个分频比为12的方波输出分频器,并用实验来 检测设计是否正确。 2.用VHDL语言和PLD设计一个序列信号检测器,当序列信号检测器连续收到一组1110010数码后,输出为1;否则输出为0,并用实验来证明设计正确。 |

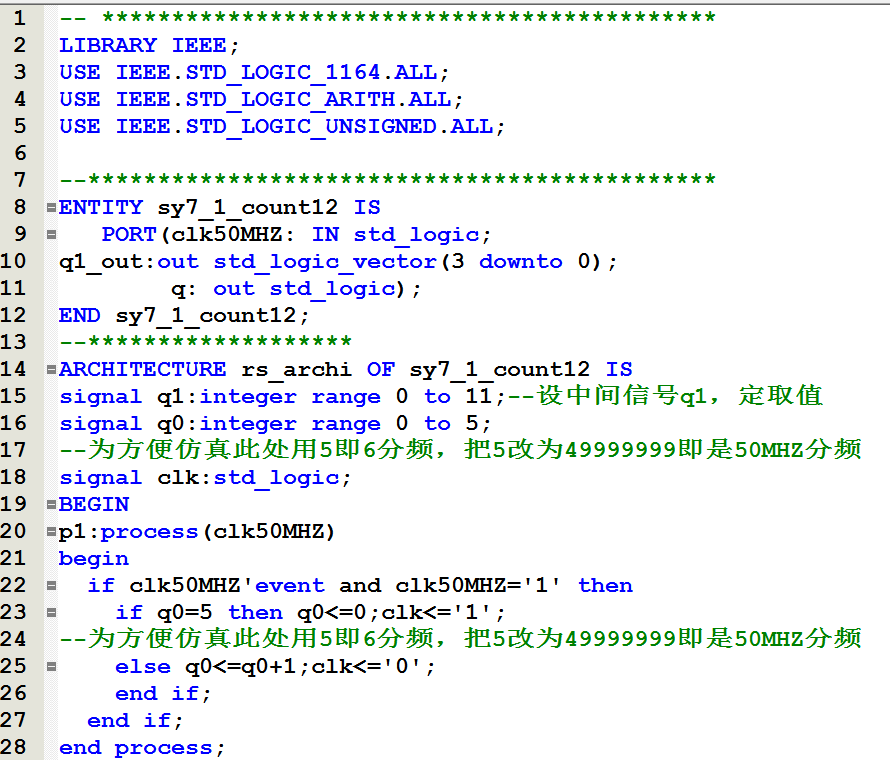

一、分频比为12的方波输出分频器:

本设计分两个进程,第一个进程是1秒分频设计,第二个进程是12分频器设计。注意:第16、23行仿真时用5,下载时改为49999999。

添加实验板上50MHZ分频时钟的方法,引脚分配时clk50MHZ分配给表7-6的PIN_E1:

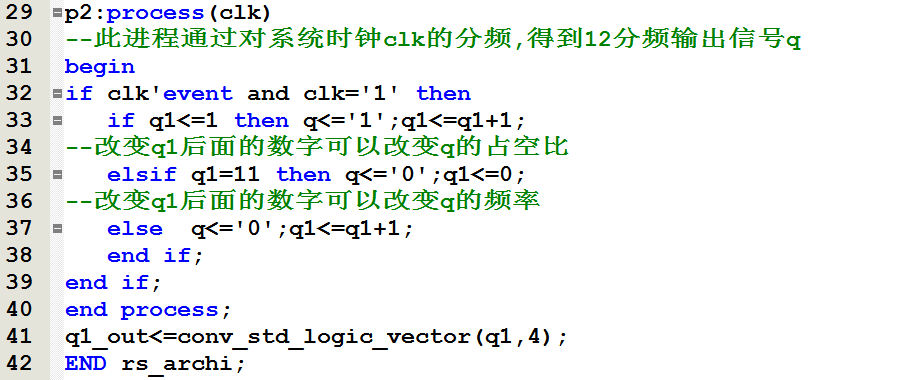

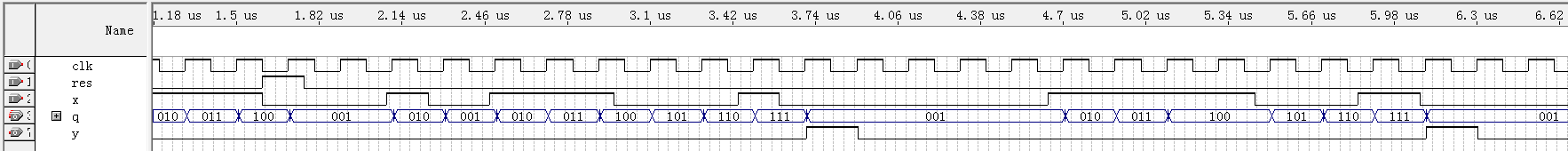

3.仿真结果:

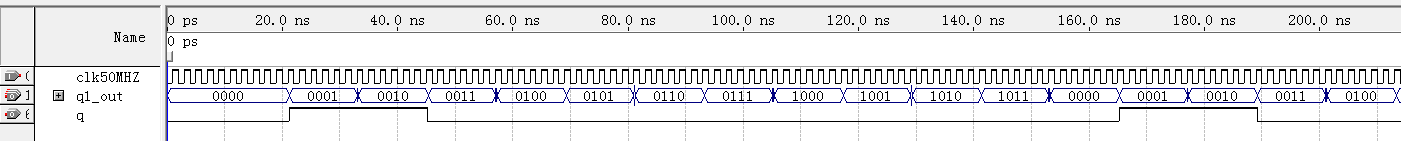

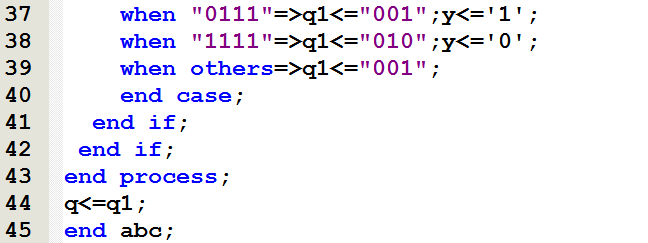

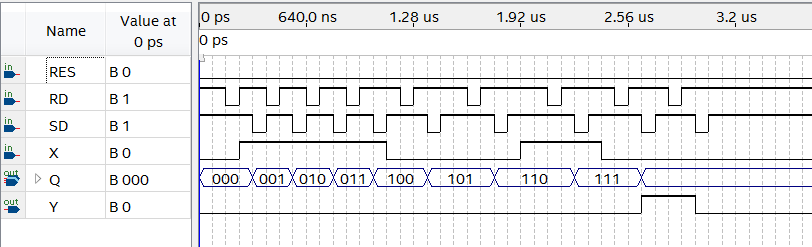

二、序列信号检测器:

1.序列信号检测电路:

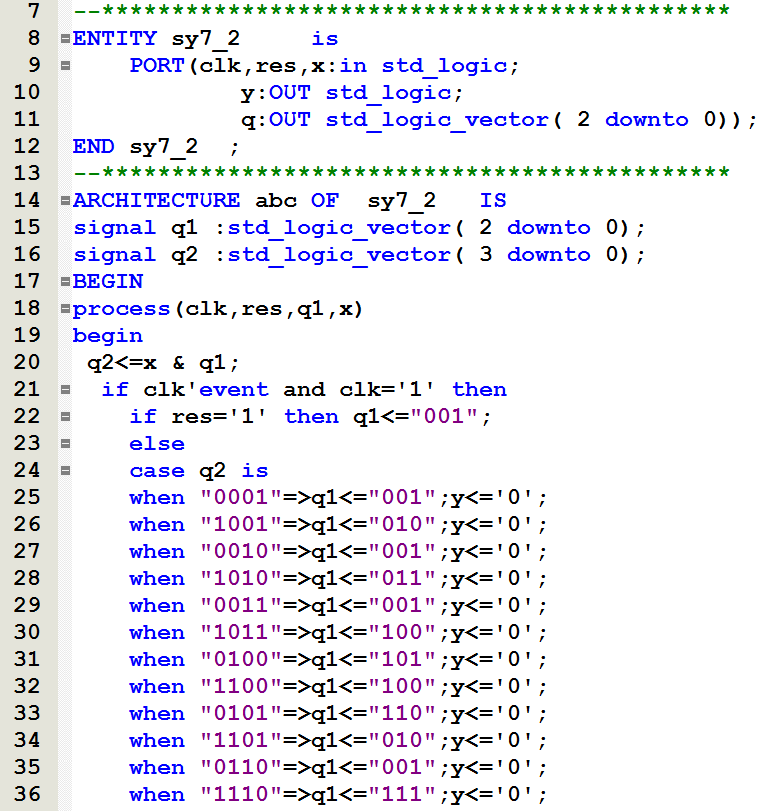

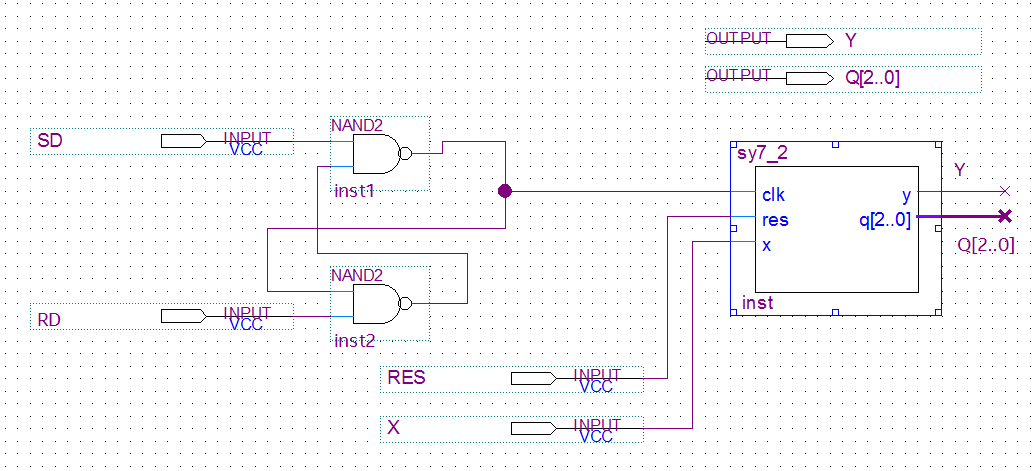

2.总电路:

如果把时钟输入信号分配在按键上,由于实验板上按键抖动,会造成一次按键动作输出多个CLK时钟。用时钟信号前添加RS触发器方法去除抖动,确保每次按键动作仅输出一个有效时钟CLK的跳变,操作方法是分别按下R和S,可以获得一次上跳变,以此类推。图中与非门符号:NAND2,双击电路图空白处在对话框里填写NAND2即可调出。

三、实验原理视频:用QUARTUSII18.1后,参考以下“四、实验七任务一原理续”和“五、实验七任务二原理”。

四、实验七任务一原理续:

五、实验七任务二原理: