实验十一 MSI计数器的应用(二)

上一节

下一节

实验项目 | MSI计数器的应用(二) |

实验目的 | 1.掌握MSI计数器的逻辑功能和主要应用。 2.熟悉用MSI计数器组成任意进制计数器以及序列信号发生器的方法。 |

实验要求 | 掌握MSI计数器的应用 |

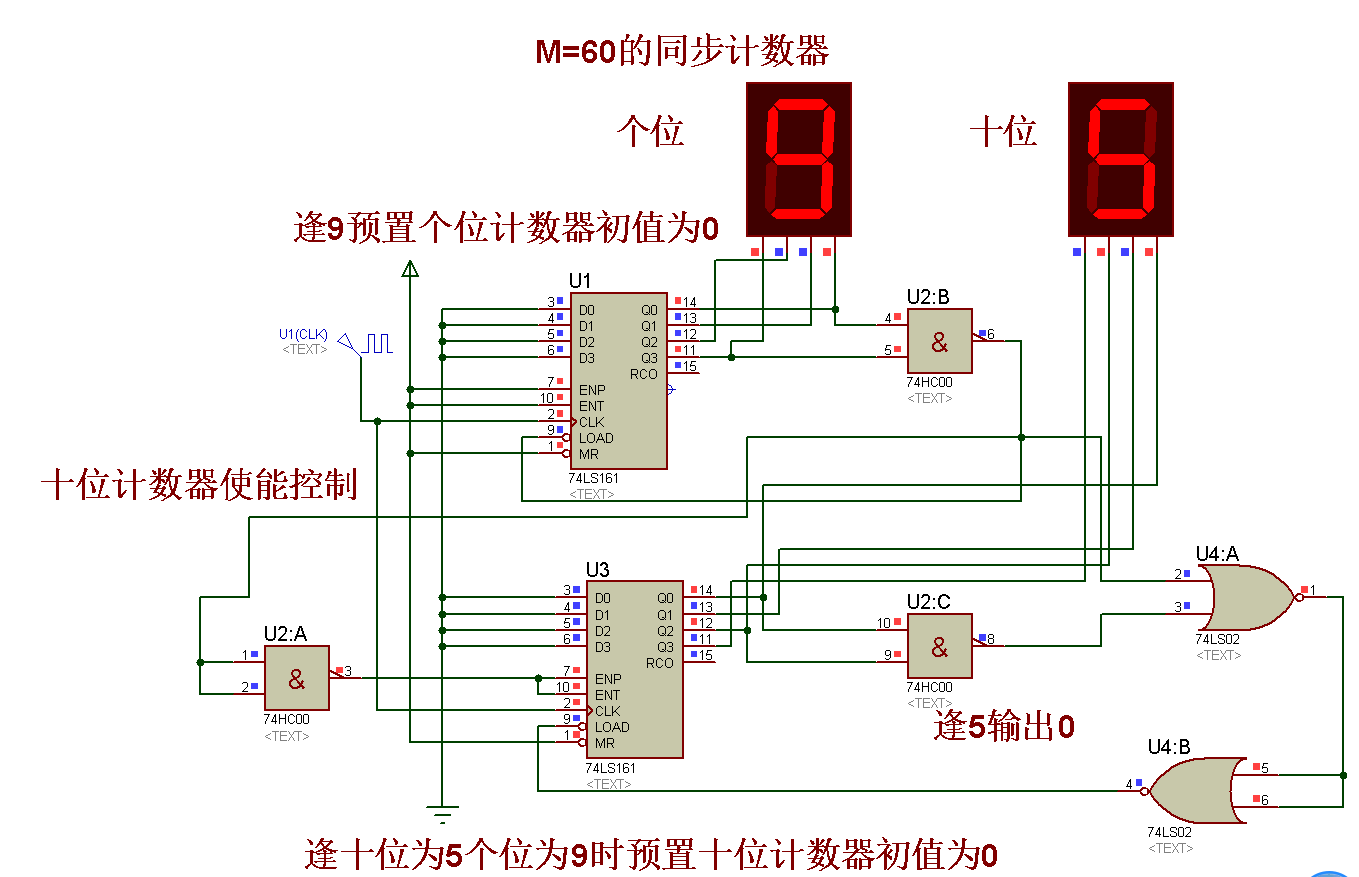

实验内容 | 用MSI计数器组成一个起始状态为0的60进制同步加法计数器,并测试其输入和输出的同步波形,以检测电路的逻辑功能是否正确。 |

一、实验内容:

1.用中、小规模芯片在面包板上搭接的实验方法:

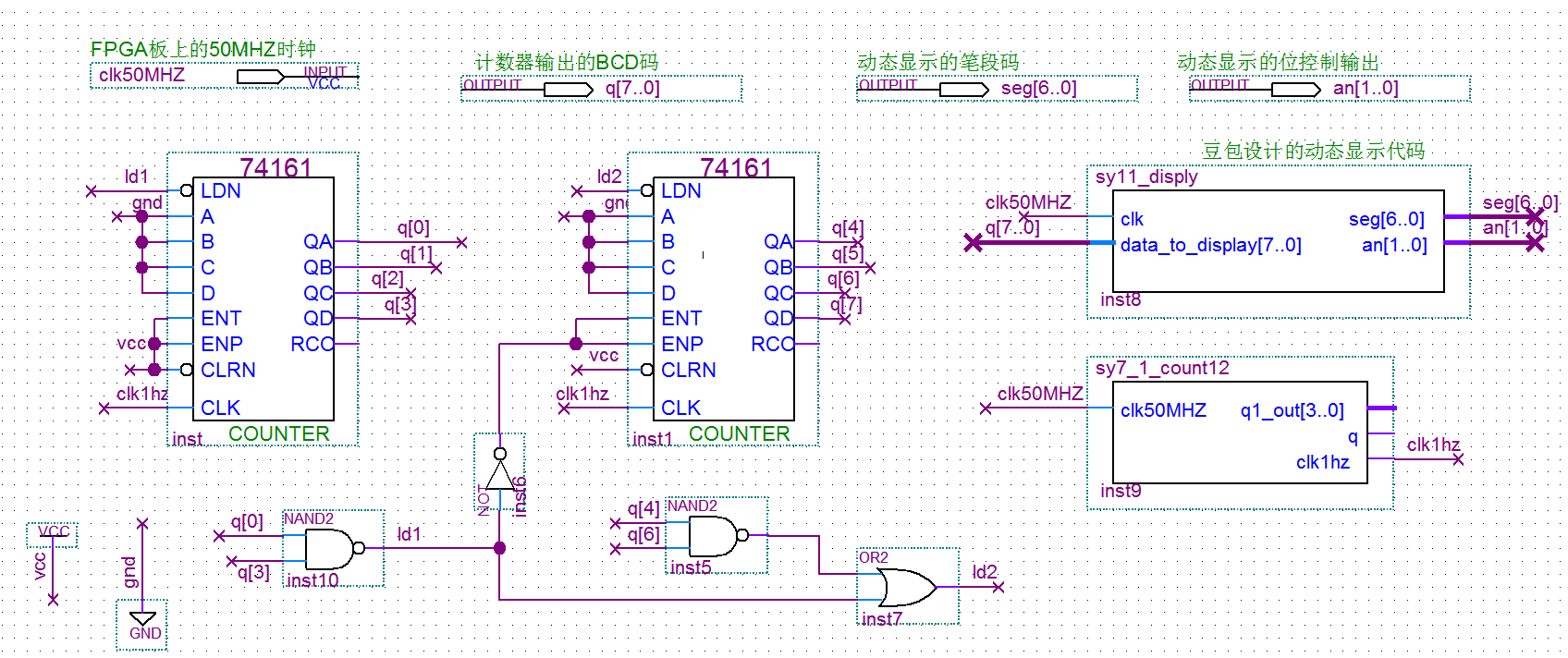

2.用FPGA板:

(1)实验电路图:

(2)计数器的1HZ计时时钟,由实验七的任务一修改获得,把原代码中的中间信号clk送到输出引脚clk1hz,作为计数器时钟。

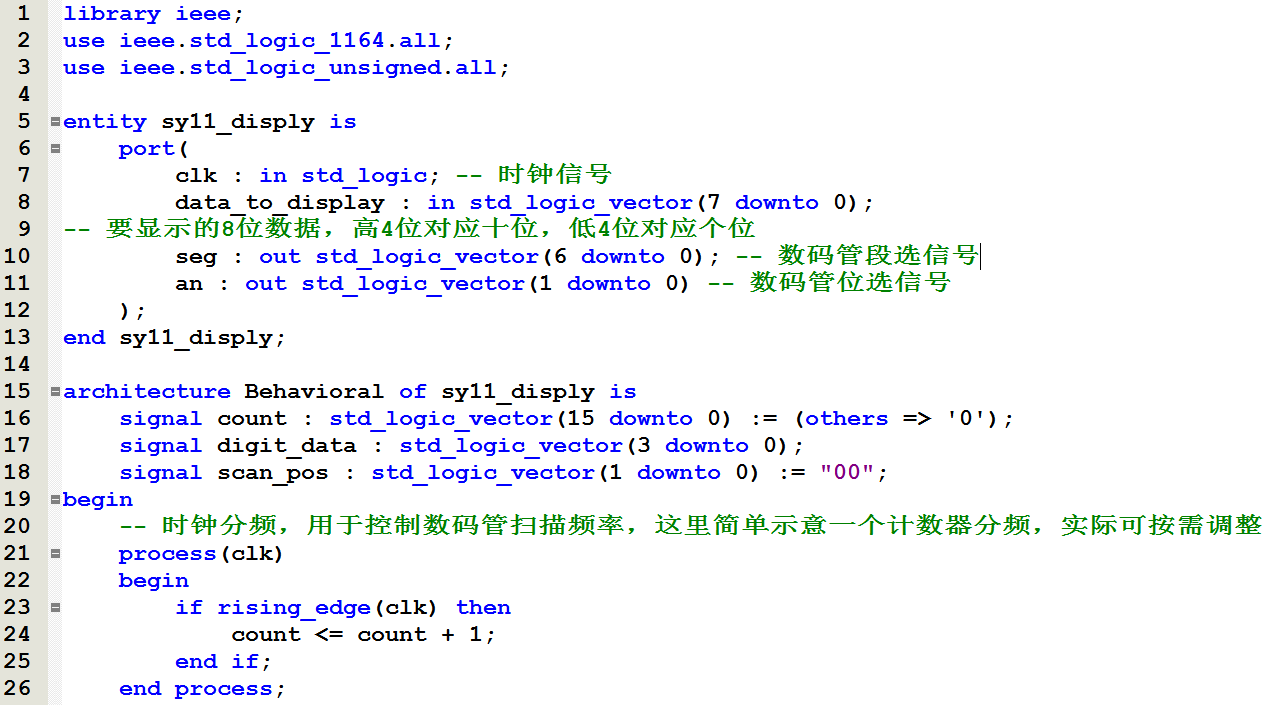

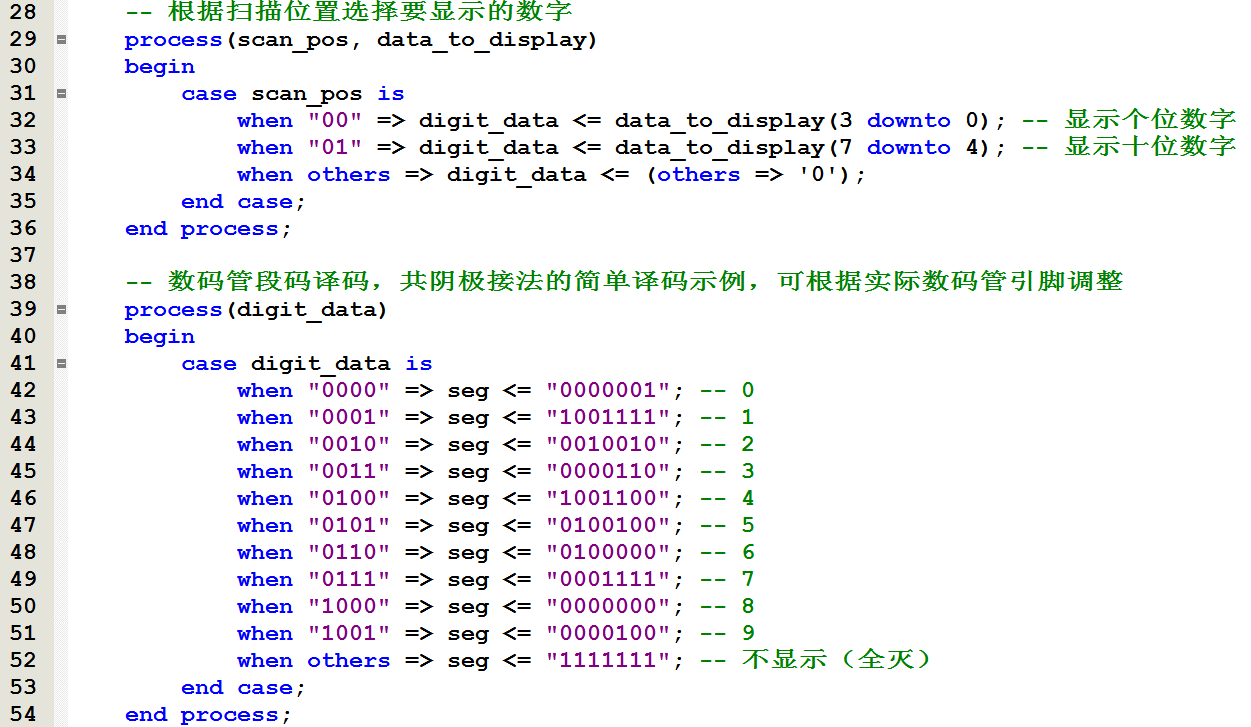

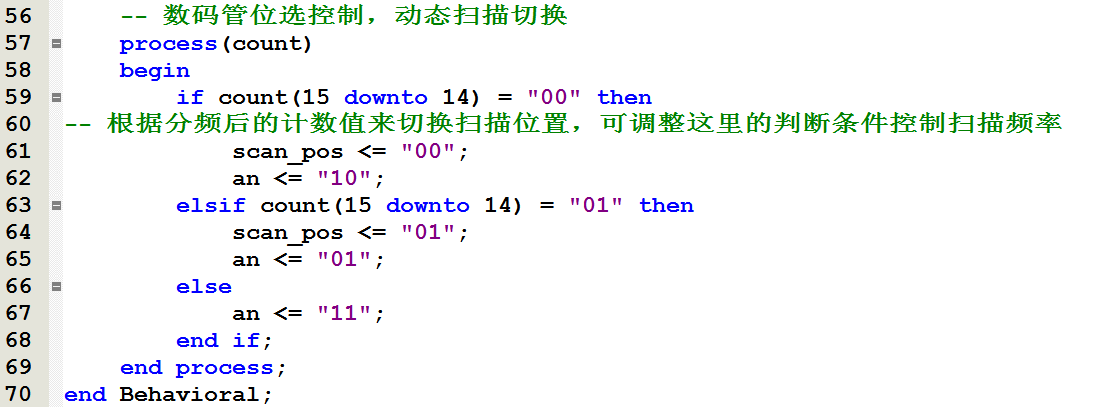

(3)两位动态显示程序,用豆包设计的代码。

(4)仿真时,实验七任务一模块的分频比设小些,观测计数器输出的BCD码q[7..0]引脚波形是否符合M=60的加一计数器功能,下载时分频比恢复为49999999,同时观测下载后动态显示效果是否正确。

二、实验原理视频: