指令周期

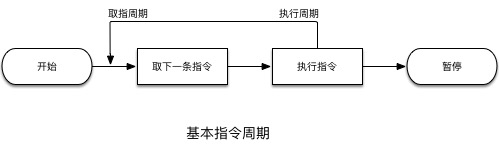

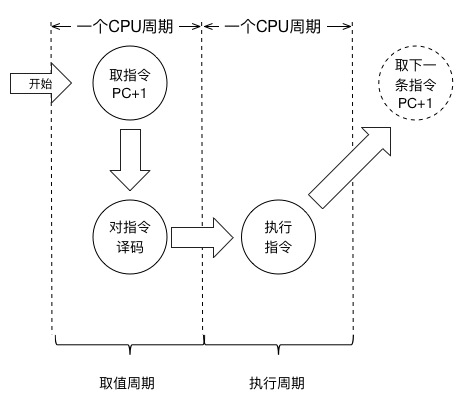

CPU每取出一条指令并执行这条指令,都要完成一系列的操作,这一系列的操作所需的时间通常叫做一个指令周期。换言之,指令周期是取出一条指令并执行这条指令的时间。

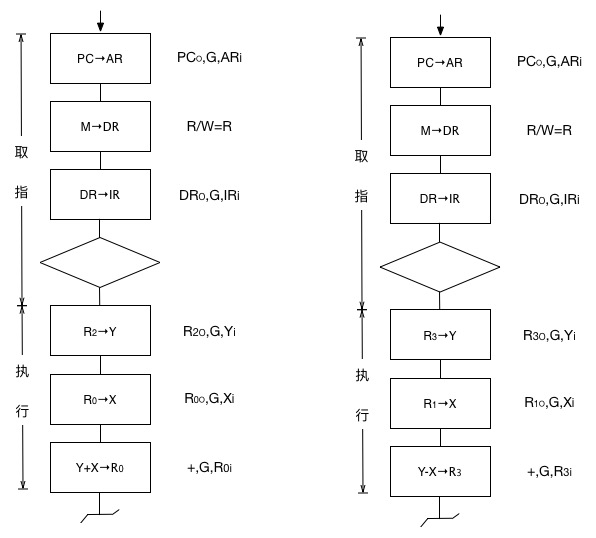

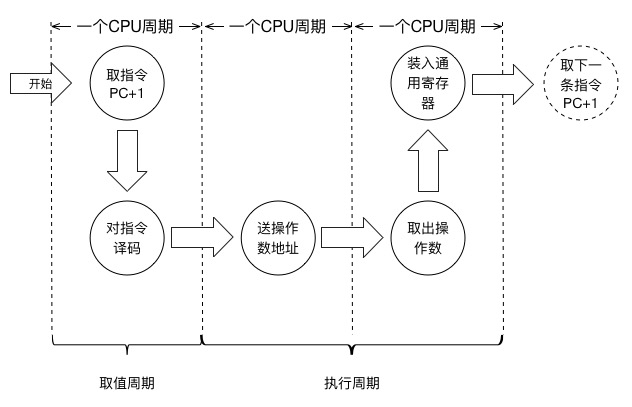

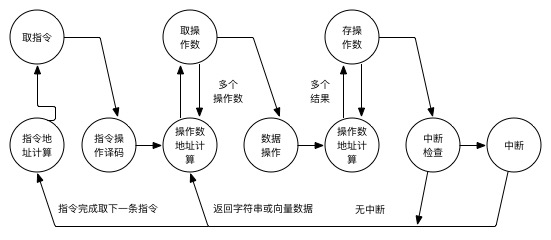

图6.4-1 基本指令周期

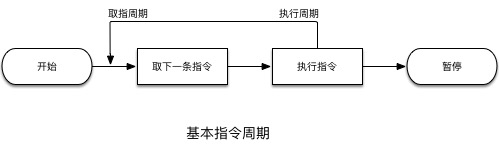

图6.4-2 指令周期状态图

表5.1 列出了由6条指令组成的一个简单程序。其中既有RR型指令,又有RS型指令;既有算术逻辑指令,又有访存指令。

指 令 存 储 器 | 八进制地址 | 指令助记符 | 说明 |

100 101 102 103 104 105 106 |

MOV RO,R1 LAD R1,6 ADD R1,R2 STO R2,(R3) JMP 101 AND R1,R3 | 程序执行前(R0)=00,(R1)=10,(R2)=20,(R3)=30 传送指令MOV执行(R1)→R0 取数指令LAD从数存6号单元取数(100)→R1 加法指令ADD执行(R1)+(R2)→R2,结果为(R2)=120 存数指令STO用(R3)间接寻址,(R2)=120写入数存30号单元 转移指令JMP改变程序执行顺序到101号单元 逻辑乘AND指令执行(R1)·(R3)→R3

|

数据存储器 | 八进制地址 | 八进制数据 | 说明 |

5 6 7 10 · · · 30 | 70 100 66 77 · · · 40(120) |

执行LAD指令后,数存6号单元的数据100仍保存在其中

执行STO指令后,数存30号单元的数据由40变为120 |

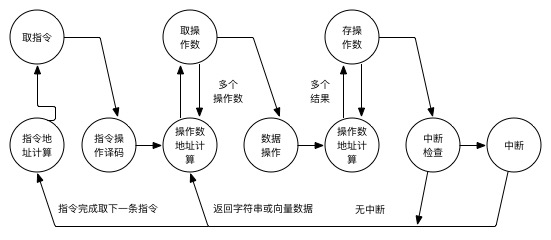

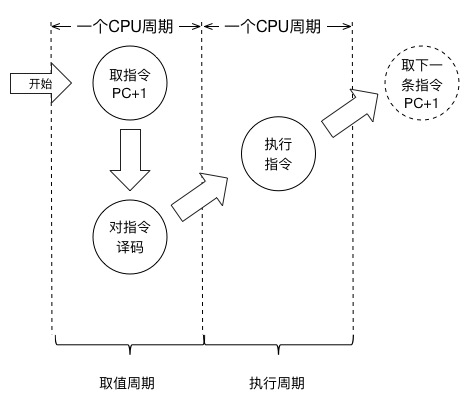

MOV指令的指令周期

MOV是一条RR(寄存器-寄存器)型指令,需要两个CPU周期,其中取指周期需要一个CPU周期,执行周期需要一个CPU周期。

图6.4-3 MOV指令的指令周期

取指周期中CPU完成三件事:

从指存中取出指令;

对程序计数器PC加1,以便为取下一条指令做好准备;

对指令操作码进行译码或测试,以便确定进行什么操作;

执行周期中CPU根据对指令操作码的译码或测试,进行指令所要求的操作。对MOV指令来说,执行周期完成两个通用寄存器 、

、 之间的数据传送操作。

之间的数据传送操作。

取指周期:

程序计数器PC中状图第一条指令地址101(八进制)

PC的内容被放到指令地址总线ABUS(I)上,对指存进行译码,并启动读命令;

从101号地址读出的MOV指令通过指令总监IBUS装入指令寄存器IR;

程序计数器内容加1,变成102,为取下一条指令做好准备;

指令寄存器中的操作码(OP)被译码;

CPU识别出是MOV指令。至此,取指周期执行结束;

执行周期

操作控制器(OC)送出控制信号到通用寄存器,选择 (10)作源寄存器,选择

(10)作源寄存器,选择 (10)作目标寄存器;

(10)作目标寄存器;

OC送出控制信号到ALU,指定ALU做传送操作;

OC送出控制信号,打开ALU输出三态门,将ALU输出送到数据总监DBUS上。注意,任何时候DBUS上只能有一个数据;

OC送出控制信号,将DBUS上的数据打入到数据缓冲寄存器DR(10);

OC送出控制信号,将DR中的数据10打入到目标寄存器 ,

, 的内容由00遍为10。

的内容由00遍为10。

至此,MOV指令执行结束。

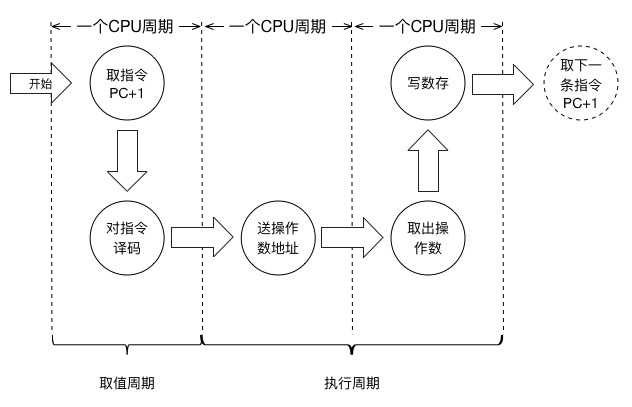

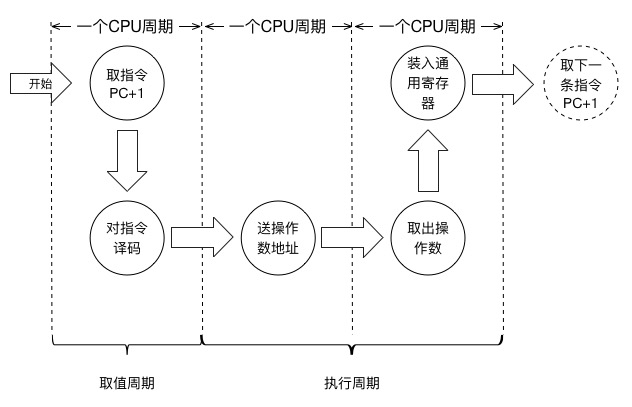

LAD指令的指令周期

LAD指令是RS型指令,它先从指令存储器取出指令,然后从数据存储器6号单元取出数据100装入通用寄存器 ,原来

,原来 中存放的数据10被更换成100.由于一次访问指存,一次访问数存,LAD指令的指令周期需要三个CPU周期。

中存放的数据10被更换成100.由于一次访问指存,一次访问数存,LAD指令的指令周期需要三个CPU周期。

图6.4-4 LAD指令的指令周期

取指周期

CPU的动作完全与MOV指令取指周期中一样,只是PC提供的指令地址为102,按此地址从指令存储器读

ADD指令的指令周期

ADD指令是RR型指令,在运算器中用两个寄存器 和

和 的数据进行加法运算。指令周期只需两个CPU周期,其中一个是取指周期,和MOV指令相同,执行周期完成的动作如下:

的数据进行加法运算。指令周期只需两个CPU周期,其中一个是取指周期,和MOV指令相同,执行周期完成的动作如下:

(1)操作控制器OC送出控制命令到通用寄存器,选择 做源寄存器,

做源寄存器, 做目标寄存器;

做目标寄存器;

(2)OC送出控制命令到ALU,制定ALU做 (100)和

(100)和 (20)的加法操作;

(20)的加法操作;

(3)OC送出控制命令,打开ALU输出三态门,运算结果120放到DBUS上;

(4)OC送出控制命令,将DBUS上数据打入缓冲寄存器DR;ALU产生的进位信号保存状态字寄存器在PSW中;

(5)OC送出控制命令,将DR(120)装入 ,

, 中原来的内容20被冲掉。至此,ADD指令执行周期结束。

中原来的内容20被冲掉。至此,ADD指令执行周期结束。

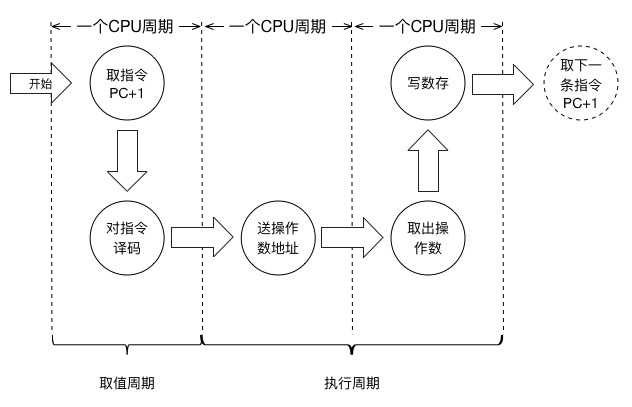

STO指令的指令周期

STO指令是RS型执行,它先方位指存取出STO指令,然后按( )=30地址访问数存,将(

)=30地址访问数存,将( )=120写入到30号单元。由于一次访问指存,一次访问数存,因此指令周期需3个CPU周期,其中执行周期为2个CPU周期,取指周期和MOV指令相同,执行周期为2个CPU周期,CPU完成如下动作:

)=120写入到30号单元。由于一次访问指存,一次访问数存,因此指令周期需3个CPU周期,其中执行周期为2个CPU周期,取指周期和MOV指令相同,执行周期为2个CPU周期,CPU完成如下动作:

图6.4-5 STO指令的指令周期

(1)操作控制器OC送出操作命令到通用寄存器,选择( )=30做数据存储器的地址单元;

)=30做数据存储器的地址单元;

(2)OC发出操作命令,打开通用寄存器输出三态门(不经ALU以节省时间),将地址30放到DBUS上;

(3)OC发出操作命令,将地址30打入AR,并进行数存地址译码;

(4)OC发出操作命令到通用寄存器,选择( )=120,作为数存的写入数据;

)=120,作为数存的写入数据;

(5)OC发出操作命令,打开通用寄存器输出三态门,将数据120放到DBUS上;

(6)OC发出操作命令,将数据120写入数存30号单元,它原先的数据40被冲掉。至此,STO指令执行周期结束。

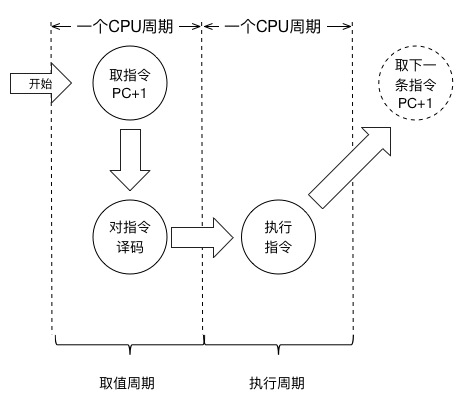

JMP指令的指令周期

JMP指令是一条无条件转移指令,用来改变程序的执行顺序。指令周期为两个CPU周期。一个取指周期,一个执行周期。

图6.4-6 JMP指令的指令周期

(1)OC发出操作控制命令,打开指令寄存器IR的输出三态门,将IR中的地址吗101 发送到DBUS上;

(2)OC发出操作控制命令,将DBUS上的地址吗101打入到程序计数器PC中,PC中的原先内容106被更换。于是下一条指令不是从106号单元取出,而是转移到101号单元取出。至此JMP指令执行周期结束。

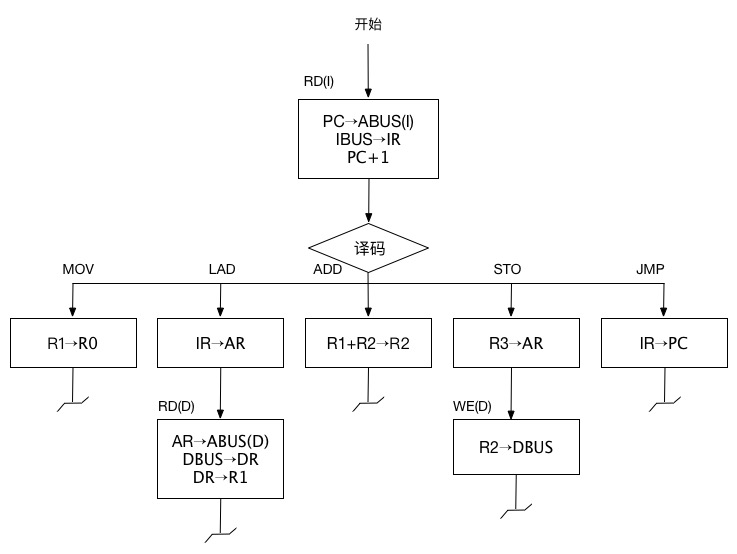

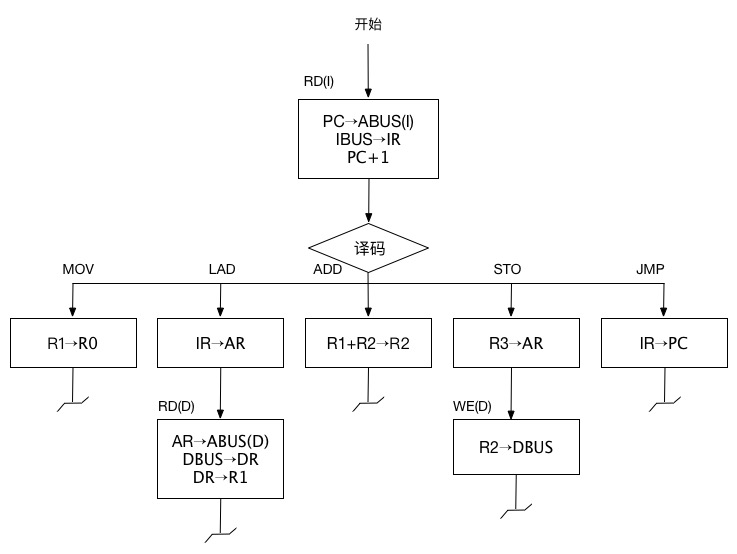

用方框图语言表示指令周期

在进行计算机设计时,一个方框代表一个CPU周期,方框中的内容表示数据通路的操作或某种控制操作。除了方框以外,还需要一个菱形符号,它通常用来表示某种判别或测试,不过时间上它依附于紧接它的前面一个方框的CPU周期,而不单独占用一个CPU周期。符号“~”为公操作符号。这个符号表示已经执行完毕,转入公操作。所谓公操作,就是一条指令执行完毕后,CPU所开始的一些操作,这些操作主要是CPU对外围设备请求的处理,如中断处理、通道处理等。由于所有指令的取指周期是完全一样的,因此,取指令也可认为是公操作。一条指令执行结束后,如果没有外设请求,CPU一定转入“取指令”操作。

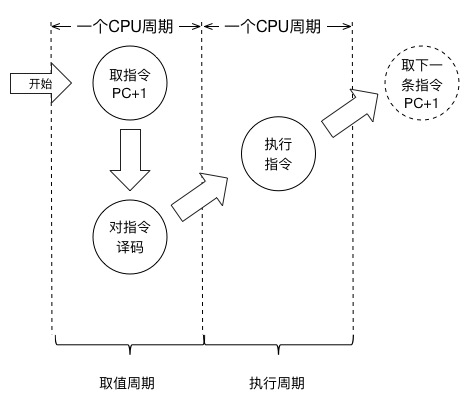

图6.4-7 用方框图语言表示指令周期

图6.4-7 用方框图语言表示指令周期

把前面的五条典型指令用方框图语言表示的指令周期如图所示。所有指令的取指周期是完全相同的,而且是一个CPU周期。指令的执行周期,由于各条指令的功能不同,所用的CPU周期是各不相同的,其中MOV、ADD、JMP指令是一个CPU周期;LAD和STO指令是两个CPU周期。图中DBUS代表数据总线,ABUS(D)代表数存地址总线,ABUS(I)代表指存地址总线,RD(D)代表数存读命令,WE(D)代表数存写命令,RD(I)代表指存读命令。

例题

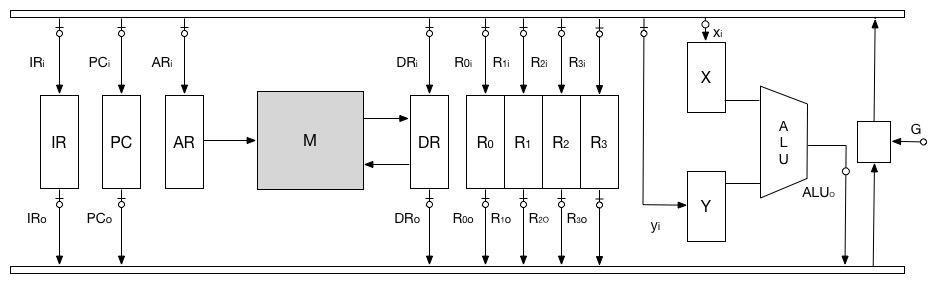

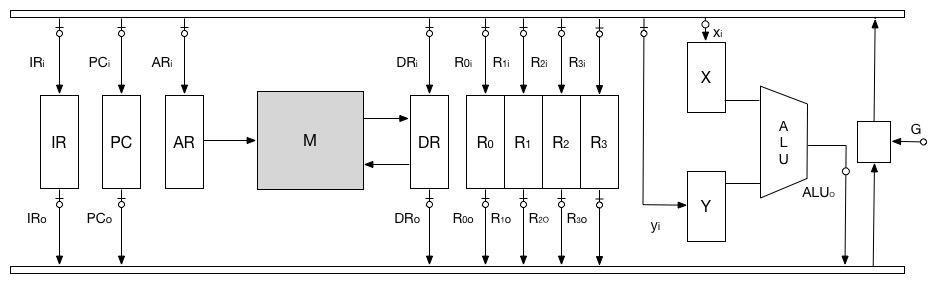

如图所示为双总线结构机器的数据通路,IR为指令寄存器,PC为程序计数器(具有自增功能),M为主存(受R/W信号控制),它既存放指令又存放数据,AR为地址寄存器,DR为数据缓存寄存器,ALU由加、减控制信号决定完成何种操作,控制信号G控制的是一个门电路,它相当于两条总线之间的桥。控制信号G控制的是一个门电路。

如图所示为双总线结构机器的数据通路,IR为指令寄存器,PC为程序计数器(具有自增功能),M为主存(受R/W信号控制),它既存放指令又存放数据,AR为地址寄存器,DR为数据缓存寄存器,ALU由加、减控制信号决定完成何种操作,控制信号G控制的是一个门电路,它相当于两条总线之间的桥。控制信号G控制的是一个门电路。

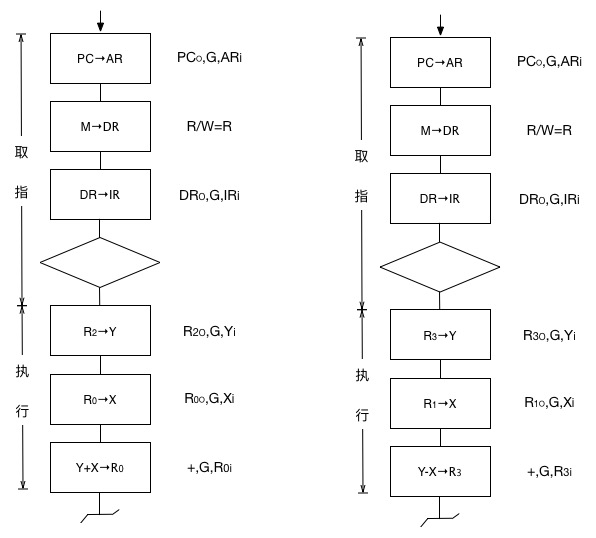

1.“ADDR2,R0”指令完成(R0)+(R2)→R0功能操作,画出其指令周期流程图,假设该指令的地址已放入PC中。并列出相应的微操作控制信号序列。

2.“SUBR1,R3”指令完成(R3)-(R1)→R3的功能操作,画出其指令周期流程图,并列出相应的微操作控制信号序列。

图6.4-8 双总线结构机器的数据通路

图6.4-8 双总线结构机器的数据通路

解:

图6.4-9 加法和减法指令的指令流程图

数据通路的功能和基本结构

数据通路的功能

数据在功能部件之间传输的路径称为数据通路。 运算器与各寄存器之间的传送路径就是中央处理器的内部数据通路。

数据通路描述了信息从什么地方开始, 中间经过哪个寄存器或多路开关,最后传送到哪个寄存器, 这些都要加以控制。

建立数据通路的任务是由“操作控制部件”来完成的。 数据通路的功能是实现CPU内部的运算器与寄存器及寄存器之间的数据交换。

数据通路的基本结构

数据通路的基本接哦古主要有以下几种:

(1) CPU内部单总线方式:将所有寄存器的输入端和输出端都连接到一条公共通路上, 这种结构比较简单, 单数据传输存在较多的冲突现象,性能较低。 连接各部件的总线只有一条时,称为单总线结构;CPU中有两条或更多的总线时,构成双总线接哦古或多总线结构。

(2)CPU内部三总线方式。 将所有寄存器的输入端和输出端都连接到多条公共通路上,相比之下单总线中的一个时钟内只允许传一个数据, 因而指令执行效率很低,因此采用多总线方式, 同时在多个总线上传送不同的数据,提高效率。

(3)专用数据通路方式:根据指令执行过程中的数据和地址的流动方向安排连接线路, 避免使用共享的总线, 性能较高, 但硬件量大。

图6.4-7 用方框图语言表示指令周期

图6.4-7 用方框图语言表示指令周期 图6.4-8 双总线结构机器的数据通路

图6.4-8 双总线结构机器的数据通路