概述

传统的DRAM是通过分页技术进行访问的。 在存取数据时,需要分别输入一个行地址和一个列地址,这会耗费时间。 快速页模式随机存储器(Fast Page Mode DRAM)是传统DRAM的改进型产品,通过保持行地址不变而改变列地址,可以对给定的行的所有数据进行更快的访问。

FPM DRAM还支持突发模式访问。所谓如噶模式是指对一个给定的访问在建立行和列地址之后,可以访问后面3个相邻的地址,而不需要额外的延迟和等待状态。

扩展数据输出(Extended Data Output DRAM, EDO DRAM)是在FPM DRAM基础上加以改进的存储器控制技术。 EDO 输出数据在整个CAS周期都是有效的,EDO不必等待当前的读写周期完成即可启动下一个读写周期 ,即可以在输出一个数据的过程中准备下一个数据的输出。 EDO DRAM采用一种特殊的主存读出控制逻辑, 在读写一个存储单元时, 同时启动下一个(连续)存储单元的读写周期,从而节省了重选地址的时间,提高了读写速度。

同步动态随机存储器(Synchromous DRAM, SDRAM)是一种与主存运行同步的DRAM. SDRAM在同步脉冲的控制下工作,取消了主存等待时间,减少了数据传送的延迟时间,因而加快了系统速度。

双数据传输率同步动态随机存储器(Double Data Rate SDRAM, DDR SDRAM)也可以说是SDRAM的升级版本,不仅能再时钟脉冲上升沿读出数据而且还能在下降沿读出数据,不需要提高时钟频率就能加倍提高SDRAM的速度。

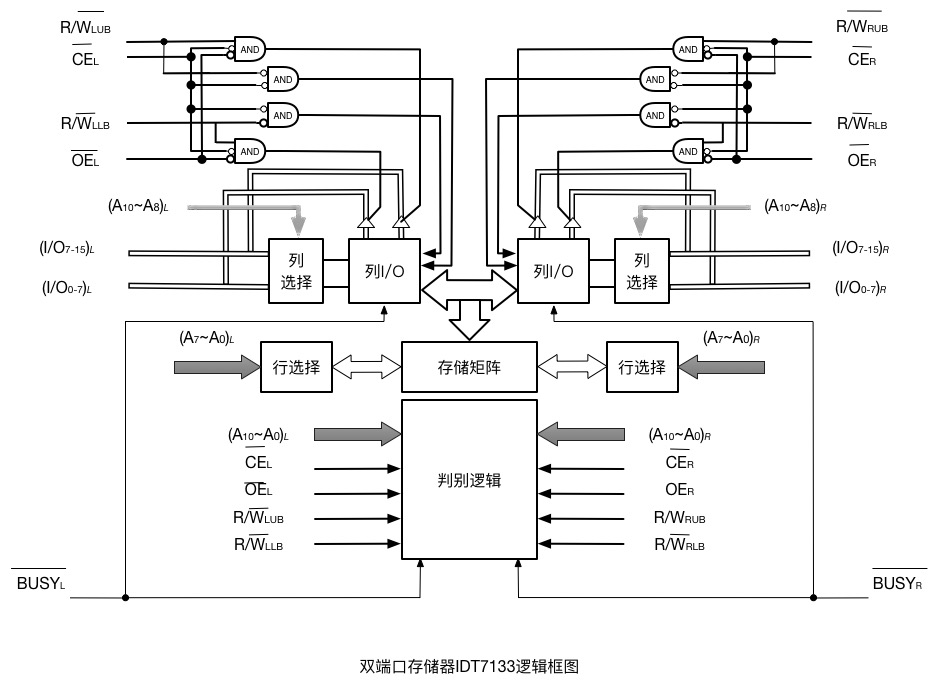

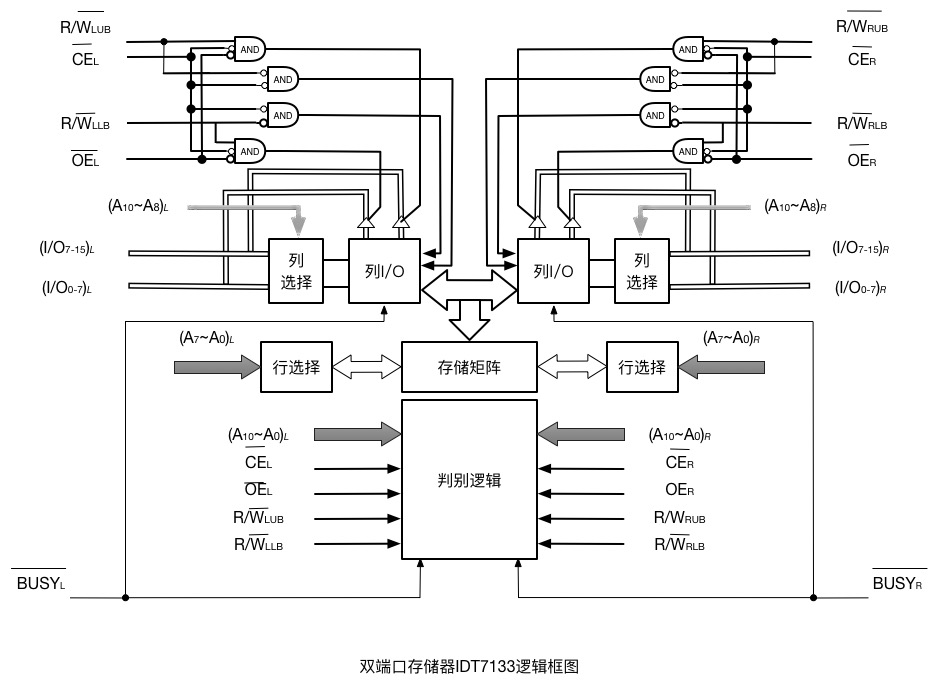

双端口存储器

双端口存储器由于同一个存储器具有两组相互独立的读写控制电路而得名。

逻辑结构

图5.3-1 双端口存储器IDT7133逻辑框图

无冲突读写控制

当两个端口的地址不相同时,在两个端口上进行读写操作,一定不会发生冲突。当任一个端口被选中驱动时,就可对整个存储器进行存取,每一个端口有自己的片选控制和输出驱动控制。 读操作时, 端口的 打开输出驱动器,有存储矩阵读出的数据就出现在I/O线上。

有冲突读写控制

当两个端口同时存取存储器同一存储单元时, 变发生读写冲突。为了解决此问题,特设置了 标志。在这种情况下, 片上的判断逻辑可以决定对哪个端口优先进行读写操作,而对另一个被延迟的端口置

标志。在这种情况下, 片上的判断逻辑可以决定对哪个端口优先进行读写操作,而对另一个被延迟的端口置 标志(

标志( 变为低电平),即暂时关闭此端口。换句话说,读写操作对

变为低电平),即暂时关闭此端口。换句话说,读写操作对 变为低电平的端口是不起作用的。 一旦优先端口完成读写操作,才将被延迟端口的

变为低电平的端口是不起作用的。 一旦优先端口完成读写操作,才将被延迟端口的 标志复位(

标志复位( 变为高电平),开放此端口,允许延迟端口进行存取。

变为高电平),开放此端口,允许延迟端口进行存取。

交叉存储器

一个由若干个模块组成的主存储器是线性编址的。这些地址在各模块中如何安排,有两种方式:一种是顺序方式,一种是交叉方式。

顺序方式

设存储器容量为32个字,分成M0、M1、M2、M3四个模块,每个模块存储8个字,访问地址按顺序分配给一个模块后,接着又按顺序为下一个模块分配访问地址,这样,存储器的32个字可由5位地址寄存器指示,其中高2位选择4个模块中的一个,低3位选择每个模块中的8个字。

交叉方式

将4个线性地址0,1,2,3依次分配给M0、M1、M2、M3四个模块,再将线性地址4,5,6,7依次分配给M0、M1、M2、M3四个模块……直到全部线性地址分配完毕为止。当存储器寻址时,用地址寄存器的低2位选择4个模块中的一个,而 用高3位选择模块中的8个字。

基本结构

主存被分为4个相互独立、容量相同的M0、M1、M2、M3四个模块。每个模块都有自己的读写控制电路、地址寄存器和数据寄存器,各自以等同的方式与CPU传送信息。

CPU同时方位四个模块,由存储器控制部件控制他们分时使用数据总线进行信息传送。这样,对每一个存储模块来说,从CPU给出访存命令知道读出信息仍然使用了一个存储周期时间,而对CPU来说,它可以在一个存取周期内连续访问四个模块。各个模块的读写将重叠进行,所以多模块交叉存储器是一种并行存储器结构。

图5.3-2 顺序方式和交叉方式的存储

假设模块自称等于数据总线宽度,模块存取一个字的存储周期为T,总线传送周期为 ,存储器的交叉模块数为m,那么为了实现流水线方式存取,应当满足:

,存储器的交叉模块数为m,那么为了实现流水线方式存取,应当满足:

即成块传送可按 间隔流水方式进行,也就是每经

间隔流水方式进行,也就是每经 时间延迟后启动下一个模块。

时间延迟后启动下一个模块。

称为交叉存取度。交叉存储器要求其模块数必须大于或等于m,以保证启动某模块后经

称为交叉存取度。交叉存储器要求其模块数必须大于或等于m,以保证启动某模块后经 时间再次启动该模块是,他的上次存取操作已经完成。 这样,连续读取m个字所需的时间为:

时间再次启动该模块是,他的上次存取操作已经完成。 这样,连续读取m个字所需的时间为:

而顺序方式存储器连续读取m个字的时间为:

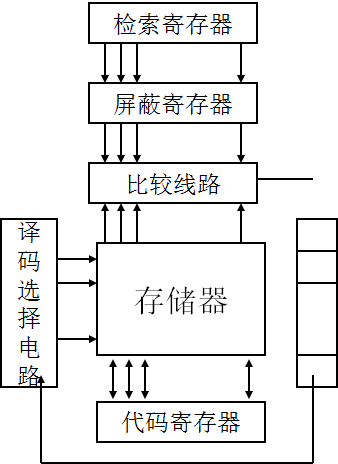

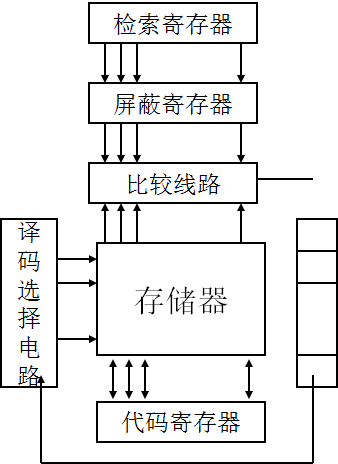

相联存储器

是按内容访问存储器。相联存储器的基本原理是把存储单元所存内容的某一部分作为检索项(即关键字项),去检索存储器,并将存储器中该检索项符合的存储单元内容进行读出或写入。

采用相联存储器可以极大地简化查找的形式和改进查找时间。

相联存储器的组成: 检索寄存器、屏蔽寄存器、符合寄存器、比较线路、代码寄存器、存储体。

图5.3-3 相联存储器逻辑图