-

1 教学内容

-

2 教学视频

-

3 翻转课堂教学任务单

-

4 翻转作业和测验

本节教学内容:

1、存储器容量的扩展

2、存储器与CPU的连接

3、存储器的校验

4、提高访存速度的措施

教学目的和要求:

1、掌握位扩展和字扩展;

2、掌握存储器三总线与CPU三总线的连接方法;

3、理解地址译码方法;

4、了解存储器的校验方法。

5、了解存储器提速的常用措施。

重点:1、存储器位扩展和字扩展

难点:1、主存储器与CPU的连接;

2、主存储体设计

第1、2讲 存储器与CPU连接、存储器校验、提高访存措施

一、知识要点

1、数据线的连接

2、地址线的连接

3、片选线的连接

4、读/写命令线的连接

5、合理选择存储芯片RAM 或ROM

6、存储器与CPU连接时的时序、负载

二、教学安排

学生先就自己在学习视频的过程中出现的问题进行提问,然后采用抢答方式为自己加分,抢答后教师对该知识点予以点评或补充。在所有学生都无法回答时,教师进行引导式的讲解;最后,采用测验的形式来检验学生学习视频的情况。翻转课分小班进行,课程主要分三个环节:

1、第一个环节:提问环节,要求学习视频时做笔记,对学习中不懂的问题进行提问,有学生能回答可加分。提问环节与以往的设计不同,以往是教师提问,抽学生回答,但是在这种情况下可能会出现学生认真学习了视频,但是知识点没有学懂而回答不上被扣分的情况,因此,根据专业特点(非技术专业)以及以鼓励为主的政策,采用了这种提问方式。

2、第二个环节:抢答环节,根据视频知识点出题,学生抢答后,对答案进行点评,正好帮助学生梳理视频中的知识,以及提醒需注意的重难点。

3、第三个环节:测验,测试题为视频相关理论内容。此环节可以检查出学生是否有认真观看视频。

通过这三个环节,既可以检验学生课前学习视频的情况,又可以让优秀的同学冒出来。

三、教学内容

1、提供三段加专题视频和课堂测验

1)数据线的连接

2)地址线的连接

3)存储器与CPU的连接示例

4)翻转课测验

2、位扩展

目前生产的存储器芯片容量有限,在字数或字长方面与实际存储器要求有所差距,所以要在字向与位向两方面进行扩充,才能满足实际存储器的要求。cpu对存储器进行读写操作时,首先由地址总线给出地址信号,然后再发出有关进行读操作与写操作的控制信号,最后在数据总线上进行信息交换。

若芯片的数据线正好8根:一次可从芯片中访问到8位数据,全部数据线与系统的8位数据总线相连

若芯片的数据线不足8根:一次不能从一个芯片中访问到8位数据,利用多个芯片扩展数据位

这个扩展方式简称“位扩展”

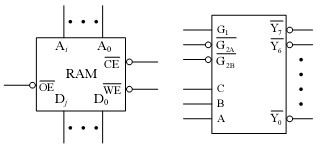

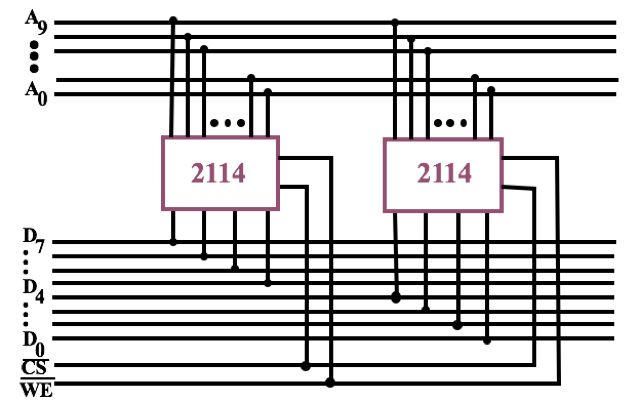

位扩展是指增加存储字长,例如,2片1KÍ4位的芯片可组成1KÍ8位的存储器,如下图所示。图中2片2114的地址线A9~A0、CS*、WE*都分别连在一起,其中一片的数据线作为高4位D7~D4,另一片的数据线作为低4位D3~D0。这样,便构成了一个1KÍ8位的存储器。

3、字扩展

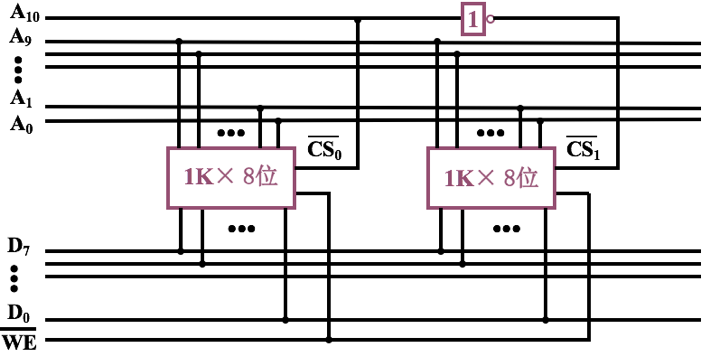

自扩展是指增加存储器字的数量。用多片位宽相同的存储器(ROM或RAM)芯片扩展包含更多存储器的过程。一般是在每个字的位数够而字的数目不够时使用。例如,用2片1KÍ8位的存储芯片可组成一个2KÍ8位的存储器,即存储字增加了一倍,如下图所示。

在此,将A10用作片选信号。由于存储芯片的片选输入端要求低电平有效,故当A10为低电平时,CS0有效,选中左边的1KÍ8位芯片;当A10为高电平时,反相后CS1有效,选中右边的1KÍ8位芯片。

4、字、位扩展

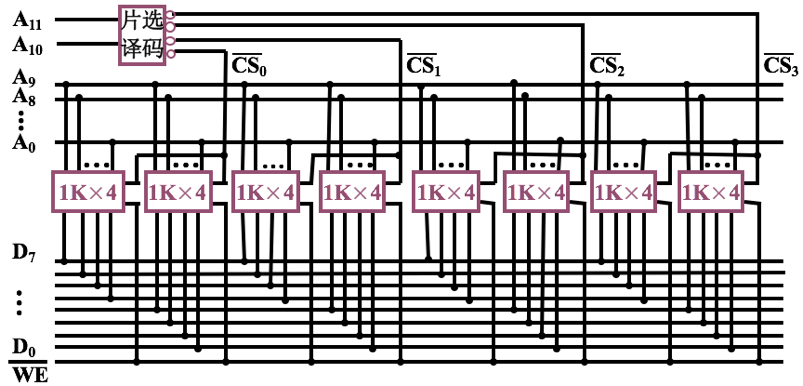

字、位扩展是指既增加存储字的数量,又增加存储字长。下图示意用8片1KÍ4位的芯片组成4KÍ8位的存储器。

由图中可见,每2片构成一组1KÍ8位的存储器,4组便构成4KÍ8位的存储器。地址线A11、A10经片选译码器得到4个片选信号CS0、CS1、CS2、CS3,分别选择其中1KÍ8位的存储芯片。WE*为读/写控制信号。

由此可见,字扩展是一种串行的扩展,而位扩展是一种并行的扩展。并行的扩展必然带来的是速度的提升,因为它使CPU一次处理的数据量成倍增加。但是有时候我们并不需要CPU一次处理太多的数据,并且每增加一倍数据量伴随的是数据线数量的成倍增长,太多的的数据线带来的必然结果是硬件成本的提高。更多的数据我们可以通过串行的方式留给CPU下次处理,所以我们现在的个人电脑字长最高也只是64位。

5、存储器与CPU的连接

存储器与CPU或系统总线的连接,这个题目很大。注意到以字节为单位组织的存储器是16位宽度、乃至32位宽度的存储器的基础,本着由易到难、由浅入深的原则,这里先考虑以字节为单位组织的存储器与8位CPU的连接,在下一节介绍16位宽度的存储器与16位CPU(以8086为例)的连接,在后面的章节再讨论32位CPU(以80386为例)的存储器组织。

在考虑存储芯片类型时,也是先考虑与CPU连接较为方便的SRAM和ROM,然后再指出DRAM与CPU连接时要特别考虑的地方。

在存储器与CPU连接时一般要考虑以下几个问题:

·CPU总线的负载能力。

·CPU与存储器速度的配合问题。

·存储器的地址空间分配。

·读/写控制信号的连接。

·数据线的连接。

·地址线的连接与存储芯片片选信号的产生。

1.CPU总线的负载能力

CPU总线的驱动能力有限,通常为一到数个,TTL负载,因此,在较大的系统中需要考虑总线驱动。一般做法是,对单向传送的地址和控制总线,可采用三态锁存器(如74LS373、8282等)和三态单向驱动器(如74LS244)等来加以锁存和驱动;对双向传送的数据总线,可采用三态双向驱动器(如74LS245、8286等)来加以驱动。三态双向驱动器也称总线收发器或数据收发器。

2.CPU与存储器速度的配合问题

每一种存储芯片都有自己固有的时序特性,这在前面已多次讲到。在和CPU相连时必须处理好时序的配合问题。处理这个问题应以CPU的时序为基准,从CPU的角度提要求。

例如,存储芯片读取时间应小于CPU从发出地址到要求数据稳定的时间间隔;存储芯片从片选有效到输出稳定的时间应小于系统自片选有效到CPU要求数据稳定的时间间隔。如果没有满足要求的存储芯片,或者出于价格因素而选用速度较慢的存储芯片时,则应提供外部电路,以产生READY信号,迫使CPU插入等待时钟Tw。看一个具体的例子,2114-2的读取时间最大为200 ns,而CPU要求的从地址有效到数据稳定的时间间隔为150 ns,则不能使用2114—2,可选用比它快的芯片。如果出于价格因素,一定要用2114—2,则需要设计READY产生电路,以便插入Tw。

3.存储器的地址空间分配

内存通常分为RAM和ROM两大部分,而RAM又分为操作系统占用区和用户区。另外,目前生产的存储器芯片,单片的容量仍然是有限的,即它的寻址空间是有限的,一般要由若干芯片组成一个存储器。所以,在和CPU连接时需进行存储器的地址空间分配,即需要事先确定每个芯片(或由“×l位”或“×4位”芯片组成的芯片组)所占用的地址空间。

4.读/写控制信号的连接

总的原则是CPU的读/写控制信号分别和存储器芯片的读/写信号输入端相连。实际上,一般存储器芯片没有读输入端,是用写无效时的片选信号兼作读信号。有的存储器芯片设有输出允许()引脚,一般将该引脚和CPU的读信号相连,以便该片被选中且读信号有效时将片内数据输出三态门打开。对于不需要在线编程的ROM芯片,不存在写信号的连接。

5.数据线的连接

这个问题与存储器的读/写宽度有关,而存储器读/写的最大宽度一般为CPU对外数据总线的位数。在考虑存储器与CPU的数据线连接时,总的原则是:如果选用芯片的芯片字和所要设计的存储器的读/写宽度相同,则直接将它的数据线分别和CPU的数据线相连;如果芯片字的位数小于所要设计的存储器的读/写宽度,则需进行“位扩展”,即用几片组合在一起,使它们的芯片字位数的总和等于存储器的读/写宽度,将它们的数据线分别和CPU的数据线按对应关系相连。

这里以8位CPU配8位宽度的存储器为例。若选用“×8位”存储芯片,则将它的8根数据线分别和CPU的8根数据线相连即可;而选用芯片字不足8位的存储芯片,则需要用几片(“×1位”芯片需8片,“×4位”位芯片需2片)才能构成一个8位宽度的存储器,这时,需将这些芯片的数据线按位的对应关系分别和CPU的8根数据线相连。

有些存储芯片,数据的输入和输出分别缓冲,一位数据设置DIN和DOUT两个数据线引脚。对于这种芯片,需将一位的DIN和DOUT引脚连起来,再和CPU的一根数据线相连。

6.地址线的连接及存储芯片片选信号的产生

一个存储器系统通常需要若干个存储芯片。为了能正确实现寻址,一般的做法是,将CPU或系统的一部分地址线(通常是低位地址线,位数取决于存储芯片的容量)连到所有存储芯片,以进行片内寻址(存储芯片内均设有地址译码器);而用另一部分地址线(高位地址线)进行芯片选择。存储器系统设计的关键在于如何进行芯片选择,即如何对高位地址译码以产生芯片的片选信号,常用以下三种方法:

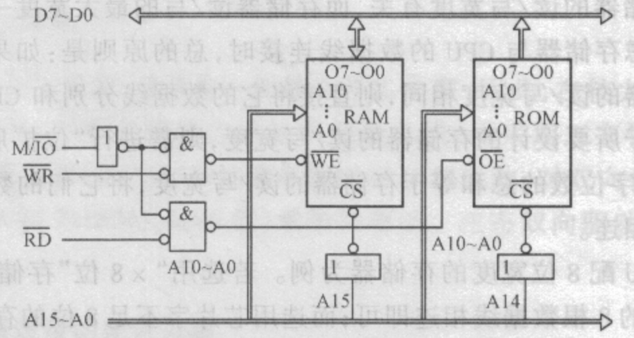

(1)线选法

用一根地址线直接作一个存储芯片的片选信号。例如,一台8位微机,有16根地址线,现要配2 KB RAM和2 KB ROM,均选用2 K×8位的芯片,则各需一片。这时可采用一种最简单的地址选择方法,如图下图所示。将CPU的地址线的低11位(A10~A0)和两个芯片的地址线分别相连,芯片的片选直接和其他的高位地址线中的一根相连,图中A15反相后接RAM的,A14反相后接ROM的。这样,A15、A14为1 0时选中RAM片,为0 1时选中ROM片。

这里分析一下RAM芯片占用地址空间的情况。未用的地址位(这里是A13~A11)通常取0,即RAM芯片的设计地址空间为8000H~87FFH。将A15、A14固定为1 0,A10一AO作片内寻址,当A13~A11取不同的组合时,可形成包括上述设计空间在内的8个区域。除去设计空间外,其他区域是:8800H~8FFFH,9000H~97FFH,…,B800H~BFFFH。由于A13~A11没有参加译码,访问这7个区域中的任何一个单元都会影响到设计空间中相应的单元,因此,这7个区域不得他用。可以认为这些区域也被该RAM芯片所占用着,称这些区域为设计空间的重叠区。对于该例中的ROM芯片,同样也存在7个重叠区,读者可自行分析。

线选法的优点是简单、无需外加选择电路;缺点是不能有效地利用地址空间,也不便于系统的扩充。该方法可用在存储容量需求小,且不要求扩充的场合,例如单片机应用系统。

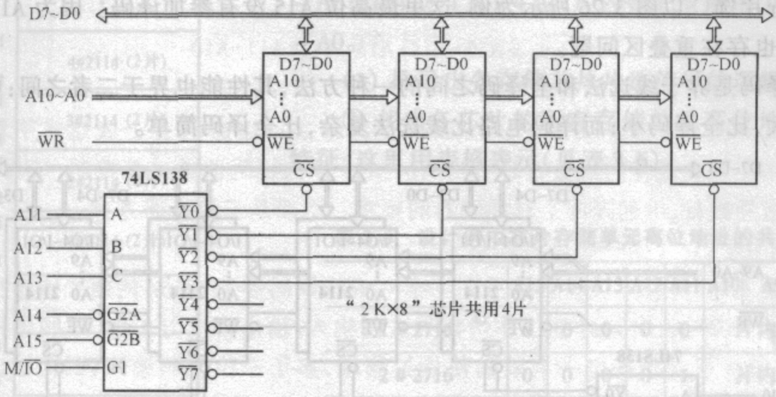

(2)全译码

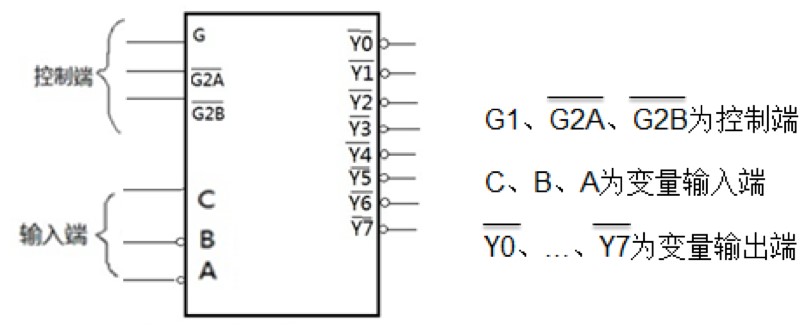

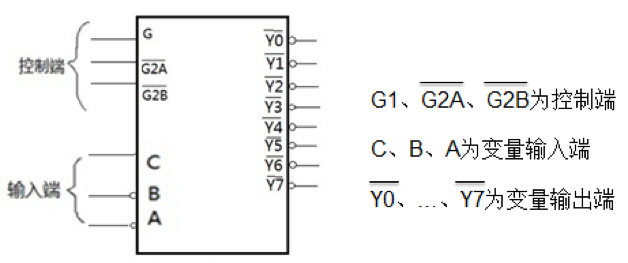

全部地址线参加译码,除去进行片内寻址的低位地址线外,其余地址线均参加译码,以进行片选。例如,一台8位微机,现要求配8 KB RAM,选用2 K×8位的芯片,安排在64 KB地址空间低端的8 KB位置。下图所示为该8 KB RAM与CPU(或系统总线)的连接。图中74Lsl38是3线一8线译码器。它有3个代码输入端c、B、A(A为低位)和8个译码输出端Y0~Y7。74LSl38还有3个使能端(或叫允许端)G1、和,第一个为高电平有效,后两个为低电平有效。只有当它们为l 0 0时,译码器才进行正常译码;否则,译码器不工作,所有的输出均无效(为高)。表3.5是74LSl38的真值表。此外,常用的3线一8线译码器还有8205,其输入/输出特性和74LS138完全一样,只是使用了另一组信号名称。

从上图中可以看到,除片内寻址的低位地址线外,高位地址都参与了译码。根据图中的接法,当A15~A1l为00000时,YO有效,选中左起第一片;为00001时,Y1有效,选中左起第二片,其他依此类推。

全译码的优点是可利用全部地址空间,可扩充性好;缺点是译码电路开销大。

(3)部分译码

它是前两种方法的综合,即除进行片内寻址的低位地址线外,其余地址线有一部分参加译码以进行片选。以下图所示为例,这里最高位A15没有参加译码。因为A15没有参加译码,所以也存在重叠区问题。

部分译码是界于线选法和全译码之间的一种方法,其性能也界于二者之间:可寻址空间比线选法大,比全译码小;而译码电路比线选法复杂,比全译码简单。

6、存储器与CPU的连接例题

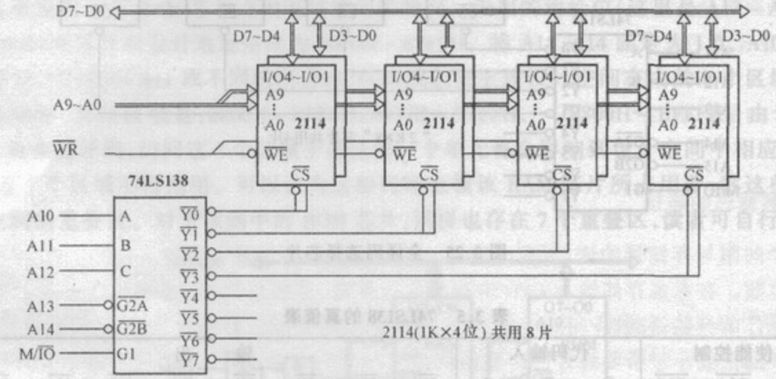

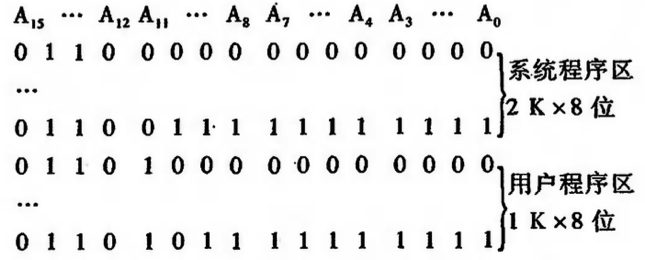

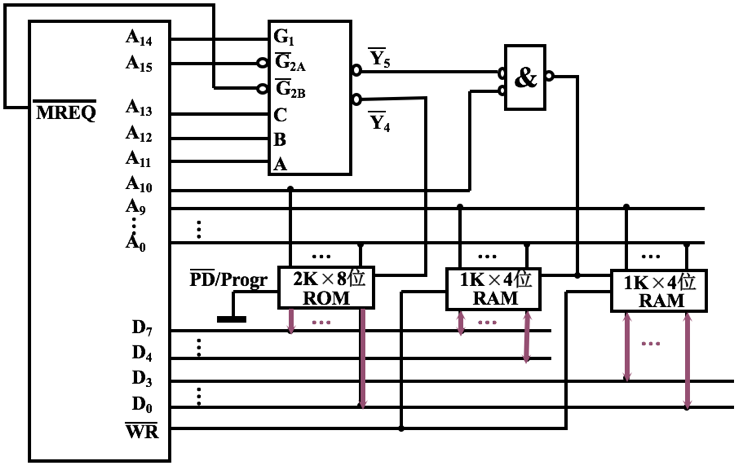

例:设CPU共有16根地址线,8根数据线,并用MREQ*作为访存控制信号(低电平有效),用WR*作为读/写控制信号(高电平为读,低电平为写)。现有下来存储芯片:1K×4位RAM,4K×8位RAM,2K×8位ROM、4K×8位ROM、8K×8位ROM及74138译码器和各种门电路,如下图,要求:

(1)主存地址空间分配:

6000H~67FFH为系统程序区。

6800H~6FFFH为用户程序区。

(2)合理选用上述存储芯片,说明各选几片。

(3)详细画出存储芯片的片选逻辑图。

解:第一步,先将十六进制地址范围写成对应的二进制地址码,并确定其总容量。

第二步,根据地址范围的容量以及该范围在计算机系统中的作用,选择存储芯片。

根据6000H~67FFH为系统程序区的范围,应选择1片2K×8位ROM,若选择4K×8位或8K×8位的ROM,都超出了2K×8的系统程序区范围。

根据6800H~6FFFH为用户程序区的范围,选2片1K×4位的RAM芯片正好满足1K×8位的用户程序区哟啊求。

第三步,分配CPU的地址线。

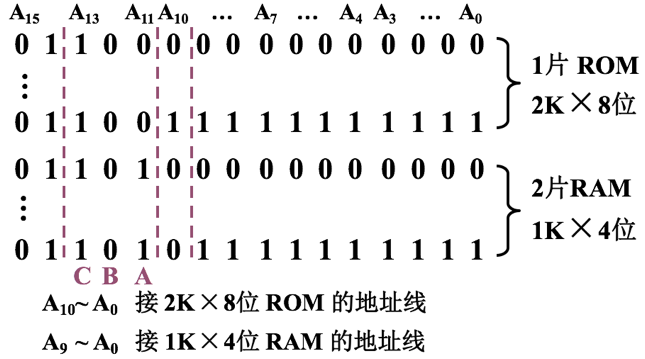

将CPU的低11位地址A10~ A0与2K×8位ROM地址线相连;将CPU的低10位地址A9~ A0与2片1K×4位RAM的地址线相连。剩下的高位地址与访存控制信号MREQ*共同产生存储芯片的片选信号。

第四步,片选信号的形成。

由给出的74138译码器图输入逻辑关系可知,必须保证控制端G1为高电平,G2A*与G2B*为低电平,才能使译码器正常工作。根据第一步写出的存储器地址范围的出,A15始终为低电平,A14始终为高电平,它们正好可分为别为译码器的G2A*(低)和G1(高)对应。而访存控制信号MREQ*(低)又正好可与G2B*对应。剩下的A13、A12、A11可分别接到译码器的C、B、A输入端。其输出Y4*有效时,选中1片ROM;Y5*与A10同时有效均为低电平时,与门输出选2片RAM,如上图所示。图中ROM芯片de PD/progr端接地,以确保在读出时低电平有效。RAM芯片读写控制端与CPU的读写命令端WR*相连。ROM的8根数据线直接与CPU的8根数据线相连,2片RAM的数据线分别与CPU数据总线的高4位和低4位相连。

四、互动及练习

本次讨论课采用提问和抢答的互动方式:

提问主要以学生提问为主,然后是教师提出视频中的一些问题进行讨论。